Intel® SHG2 DP Server Board Technical Product Specification Error Reporting and Handling

Revision 1.0 Intel Order Number C11343-001

37

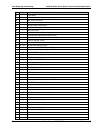

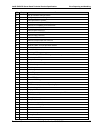

Event Trigger

Class

Event Data

Event Data 2

7:4 Optional offset from ‘Severity’ Event Trigger. (0Fh if unspecified).

3:0 Optional offset from Event Trigger for previous discrete event state. 0Fh if

unspecified.

6.3 System Management Interrupt (SMI) Handler

The SMI handler is used to handle and log system level events that are not visible to the server

management firmware. The SMI handler will preprocess all system errors; this includes errors

that are normally considered to generate an NMI. The SMI handler sends a command to the

BMC to log the event and provides the data to be logged, a Set NMI Source command to

indicate BIOS as the source of the NMI, and a BIOS LCD command to display the Liquid

Crystal Display (LCD) and LED messages. A correctable memory error does not generate an

SMI. Correctable and uncorrectable memory errors are handled and logged by the BMC.

6.3.1 PCI Bus Error

The PCI bus defines two error pins, PERR# and SERR#, for reporting PCI parity errors and

system errors, respectively.

6.3.2 Intel

Xeon

Processor Bus Error

In the case of irrecoverable errors on the host processor bus, proper execution of the SMI

handler cannot be guaranteed and the SMI handler cannot be relied upon to log such

conditions. The BIOS SMI handler records the error to the SEL only if the system has not

experienced a catastrophic failure that compromises the integrity of the SMI handler. The BIOS

always enables the error correction and detection capabilities of the processors by setting

appropriate bits in the processor model-specific register (MSR).

6.3.3 Memory Bus Error

The BMC monitors and logs memory errors. The BIOS will configure the hardware to notify the

BMC on correctable and uncorrectable memory errors. Uncorrectable errors generate an SMI

to stop the system and prevent propagation of the error. The BMC will query the hardware for

error information when notified.

6.3.4 System Limit Error

The BMC monitors system operational limits. It manages the A/D converter, defining voltage

and temperature limits as well as fan sensors and chassis intrusion. Any sensor values outside

of specified limits are fully handled by BMC, and there is no need to generate an SMI to the

host processor.

6.3.5 Processor Failure

The BIOS detects processor built-in self test (BIST) failure and logs this event. The first OEM

data byte field in the log can identify the failed processor. For example, if processor 0 fails, the