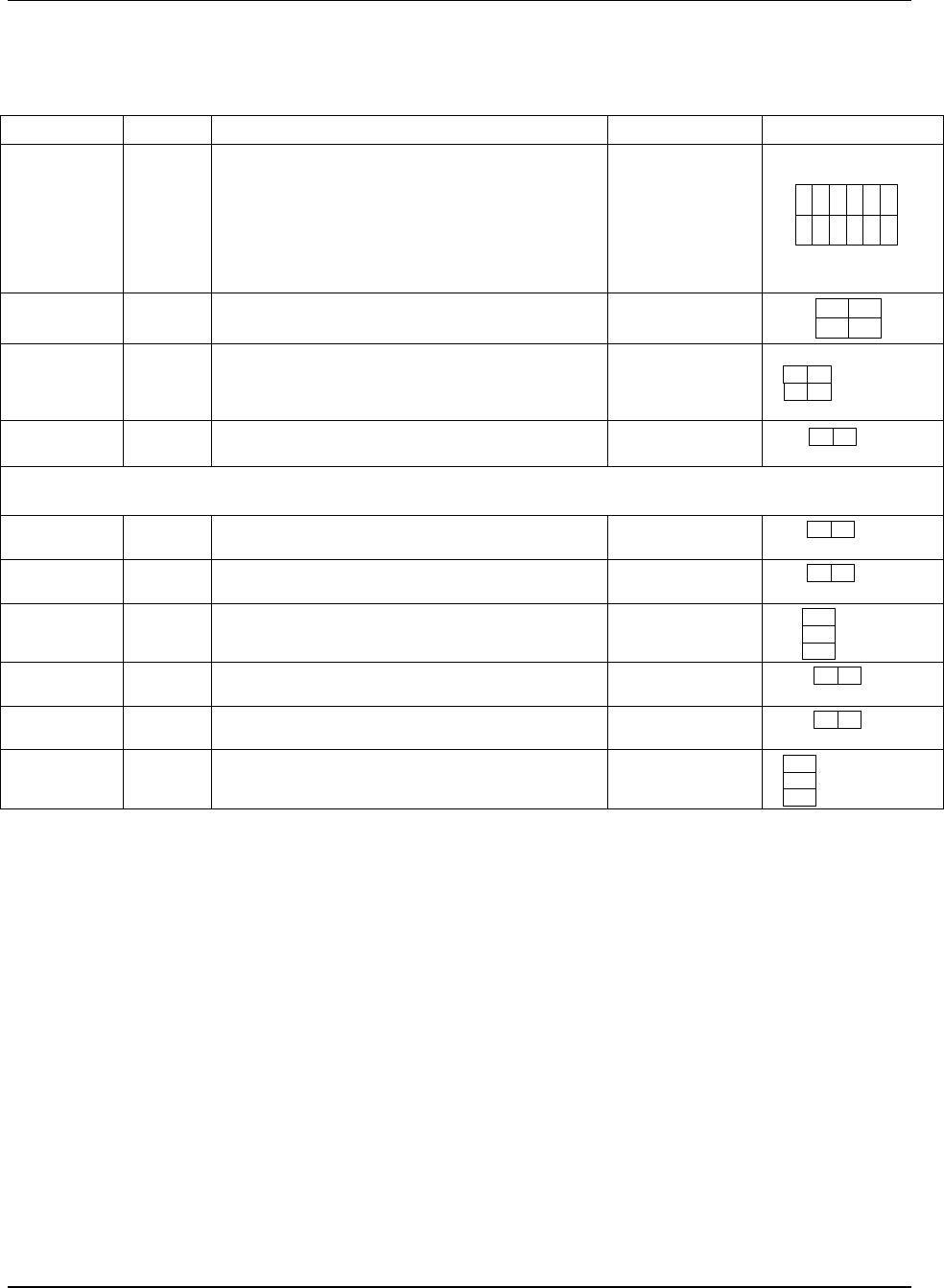

Intel® SHG2 DP Server Board Technical Product Specification Jumpers

Revision 1.0 Intel Order Number C11343-001

49

Table 33. SHG2 Configuration Jumper Options

Location Pins Feature Initial Setting

Physical Shape

CN43 1-2

3-4

5-6

7-8

9-10

11-12

CMOS Clear

Password Clear

Reserved

Reserved

Recovery Bios

Dummy

1-2 Open

3-4 Open

5-6 Open

7-8 Open

9-10 Open

11-12 Set

12 11

10 9

8 7

6 5

4 3

2 1

RSV

SIG

SIG

SIG

SIG

SIG

RSV

GND

GND

GND

GND

GND

CN27 1-2

3-4

Bios Write Protect

BMC Write Protect

1-2 Open

3-4 Open

1 2

3 4

SIG

SIG

12V

12V

CN53 1-2

3-4

PCIX1_DIS(Primary) Set: 66MHz

PCIX2_DIS(Secondary) Set: 66MHz

1-2 Open

3-4 Set

2 4

1 3

SIG SIG

GNDGND

CN58 1-2 SIDE_CI

Chassis Intrusion Detection

1-2

Connected

12

GND SIG

The following headers will be de-featured for production. These features are intended for test and evaluation only,

The headers will not be populated during production.

CN47 1-2 BMC_FRC_UPDATE

Force BMC in update mode

1-2 Open

12

SIG GND

CN48 1-2 FRB3STP

To disable FRB3_TIMER

1-2 Open

12

SIG GND

CN32 1-2

2-3

BMC Debug SRAM

BMC SRAM (Default)

2-3 Set

2

1

3

SIG

3.3V

3.3V

CN57 1-2 FP_RESETSW-00

To reset system from front panel

1-2 Open

21

SIGGND

CN56 1-2 FP_POWERSW-00

To power on/off system from front panel

1-2 Open

21

SIGGND

CN14 1-2

2-3

Use for ITP 2 Processors

Use for ITP 1 Processor

1-2 Set

2

1

3

P1_TDO

P2_TDO

P2_TDI