Server Management Intel® SHG2 DP Server Board Technical Product Specification

Intel Order Number C11343-001 Revision 1.0

32

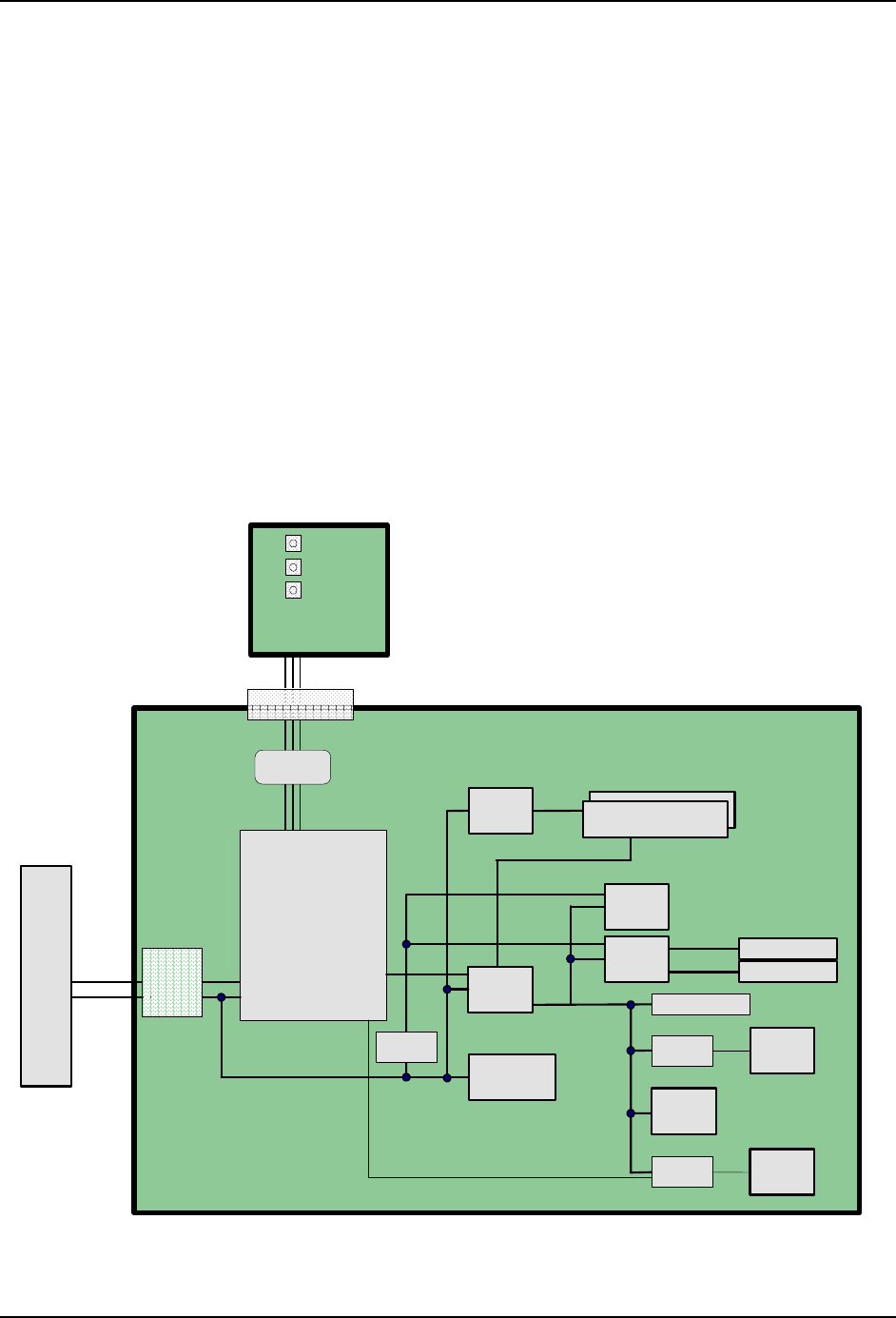

After the system is turned on, the power supply will assert the PWRGD+00 signal after all

voltage levels in the system have reached valid levels. The BMC receives PWRGD+00 and

after approximately 500 ms, asserts RST_P6_PWRGOOD, which indicates to the processors

and CSB5 that the power is stable. Upon RST_P6_PWRGOOD assertion, the CSB5 will toggle

PCI reset.

5.2.2 Hard Reset

A hard reset can be initiated by resetting the system through the front panel switch. During the

reset, the Sahalee BMC de-asserts RST_P6_PWR_GOOD. After 500 ms, it is reasserted, and

the power-up reset sequence is completed.

The Sahalee BMC is not reset by a hard reset. It may be reset at power-up.

5.2.3 Soft Reset

A soft reset causes the processors to begin execution in a known state without flushing caches

or internal buffers. Soft resets can either be generated by SIO(KBD_PINITN),

CSB5(RSB_PINITN), or by the CMIC-LE(CMIC_PINITN).

P

C

I

R

S

T

32b PCI Slots

PSON

PSU

CMIC-

LE

NIC

Hudson II/III

Front Panel

Power button

Reset button

Sleep button

Front Panel

Connector

BASEBOARD

MANAGEMENT

CONTROLLER

(BMC)

debounce

logic

Sleep

Power

Reset

PWRGD

CPURST

Processor

Processor

Video

SCSI

isolation

reset

gateing

BMC video gate

Misc

(EMP,

IPMB Isolation

logic, etc)

VRD

Pgood

logic

PLL rst

logic

CSB5

CIOB

PCIRST

PCIRST

Sec PCI Slots

Pri PCI Slots

Reset out

Pwr

Conn

GPIO

Figure 8. Basic Reset Flow