HighWire HW400c/2 User Reference Guide Rev 1.0

3.3 Computer Telephony Bus Controller

The HW400c/2 includes the Agere T8110L CT Bus Controller to control TDM bus

switching between the backplane (CompactPCI J4 connector) and the local bus,

which is connected to the JN3 connector on each of the two PTMC sites.

3.3.1 H.110 Interface (T8110L)

The Agere T8110L is a H.110 CT Bus controller that provides a complete interface

between the backplane H.110 CT bus and local PTMC CT bus through a dynamically

controllable switching fabric. The H.110 interface connects to all 32 bi-directional

TDM streams of the backplane H.110 bus via the CPCI J4 connector using the

PICMG 2.5 R1.0 standard mapping. It can access any of the 4096 time slots carried

on the H.110 bus.

The local CT bus, with 32 bi-directional TDM connections, can be programmed for

data rates of 2.048Mb/s, 4.092Mb/s or 8.192Mb/s. The local CT bus of the T8110L

is connected to each of the PTMC sites via the JN3 connectors.

The PTMC configuration 2 (PT2MC) type modules only support 20 CT bus streams, while PTMC

configuration 5 (PT5MC) modules support all 32 CT bus streams.

3.3.2 T8110L Clocking Interface (T8110L)

The T8110L LSC [3:0] output pins are connected to the PTMC Output Clock Drivers

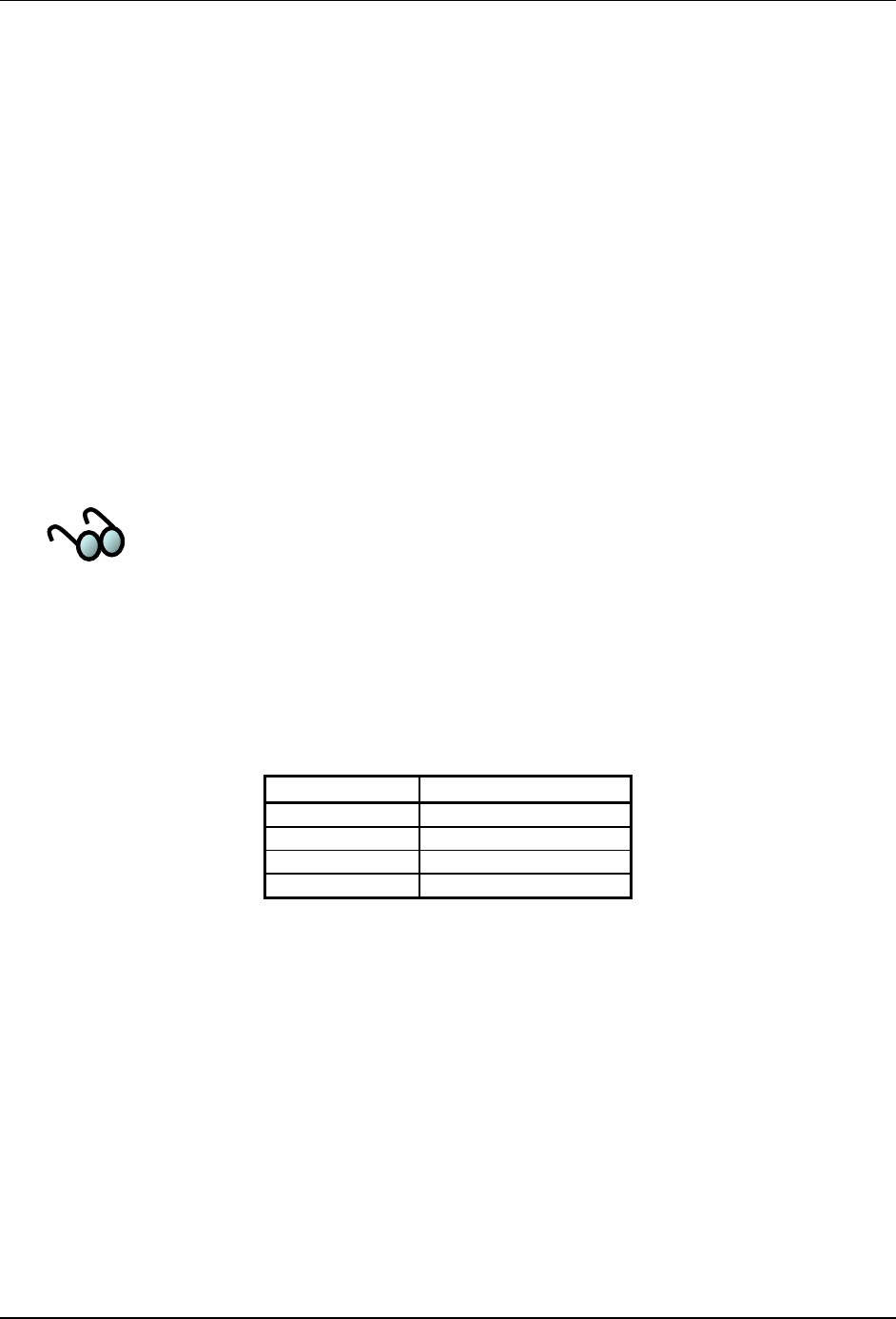

located in the CPLD. The LSC[3:0] pins are programmed as shown in Table 6.

Table 12. LSC Assignments

LSC output Signal Assignment

LSC0 CT_C8

LSC1 CT Frame

LSC2 NETREF1

LSC3 NETREF2

Figure 10 shows the local CT Bus clocking signals and how they are routed.

October 10, 2006 Copyright 2006, SBE, Inc. Page 25