HighWire HW400c/2 User Reference Guide Rev 1.0

4.2.1 Clock Select Register (CSR)

The Clock Select Register (CSR) is a Read/Write register. This register selects

whether or not the H.110 Controller (T8110L) drives the H.110 and local CT bus

sync and clock. The register bit definitions are shown in Table 30.

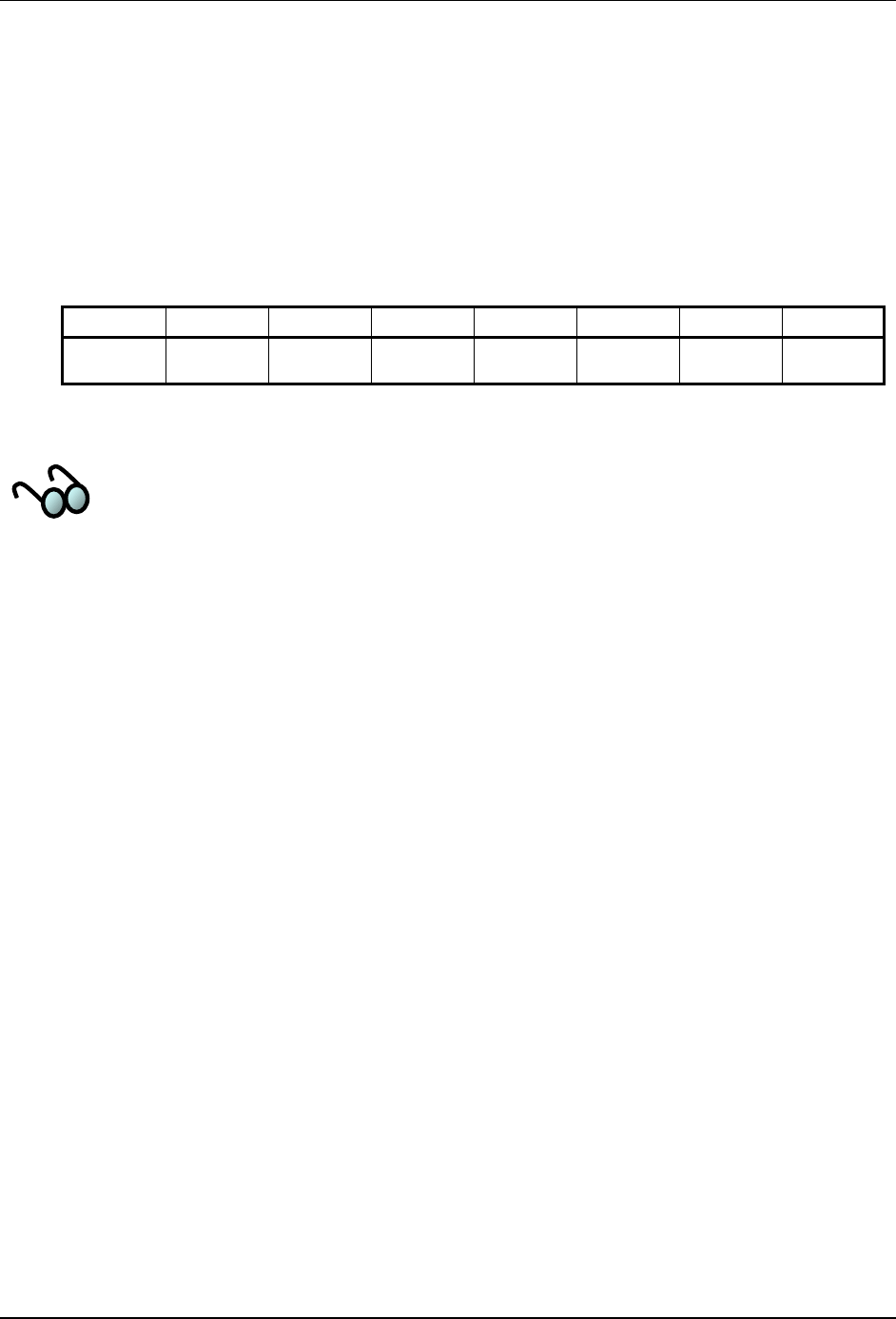

Table 30. Clock Select Register (CSR) Offset Address 0x04

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

L_ L_N

R

L_C8

S

L_C

SR

H_C H_C

e

N2-

SRC S

1-

C

A-

RC

8B-

C

8A-

SRC

8B-

SRC

Rese Rrved served

n be generated by either the HW400c/2 board or from

e re and H_C8B-SRC settings must match the

ogramming of the H.110 B ).

vely, the lo B can be enabled onto the local CT bus via the

_C8A-SRC and L_ S 8110L LSC[3:0] pins should be programmed properly prior

enabling the clock onto th local CT bus. See Section 3.3.2 for clock routing details. L_N1-SRC and

C enable N F CT bus.

_N2-SRC = L EF2 (PT_NETREF2) not driven by T8110L

= 1 Local CT Bu (PT_NETREF2) driven by T8110L

_N1-SRC = L EF1 (PT_NETREF1) not driven by T8110L

= 1 Local CT Bus NETREF1 (PT_NETREF1) driven by T8110L

_C8A-SRC = 0 Local CT Bus “A” clocks (C8A and FRAMEA) not driven by

T8110L

1 Local CT Bus “A” clocks (C8A and FRAMEA) are driven by

T8110L

_C8A-SRC = 0 H.110 “A” clocks (C8A and FRAMEA) not driven by T8110L

iven by T8110L

H_C8B-SRC = 0 H.110 “B” clocks (C8B and FRAMEB) not driven by T8110L

H.11 ocks (C8B and FRAMEB) are driven by T8

The backplane H.110 Bus “A”

the H.110 backplan

and “B” clocks ca

fore, the H_C8A-S. The RC

us Controller (T8110Lpr

Alternati cal CT us “A” and “B” clocks

L C8B- RC bits. The T

to e

L_N2-SR ETRE 1 and NETREF2 onto the local

L 0 ocal CT Bus NETR

s NETREF2

L 0 ocal CT Bus NETR

L

=

L_C8B-SRC = 0 Local CT Bus “B” clocks (C8B and FRAMEB) not driven by

T8110L

= 1 Local CT Bus “B” clocks (C8B and FRAMEB) are driven by

T8110L

H

= 1 H.110 “A” clocks (C8A and FRAMEA) are dr

= 1 0 “B” cl 110L

October 10, 2006 Copyright 2006, SBE, Inc. Page 48