HighWire HW400c/2 User Reference Guide Rev 1.0

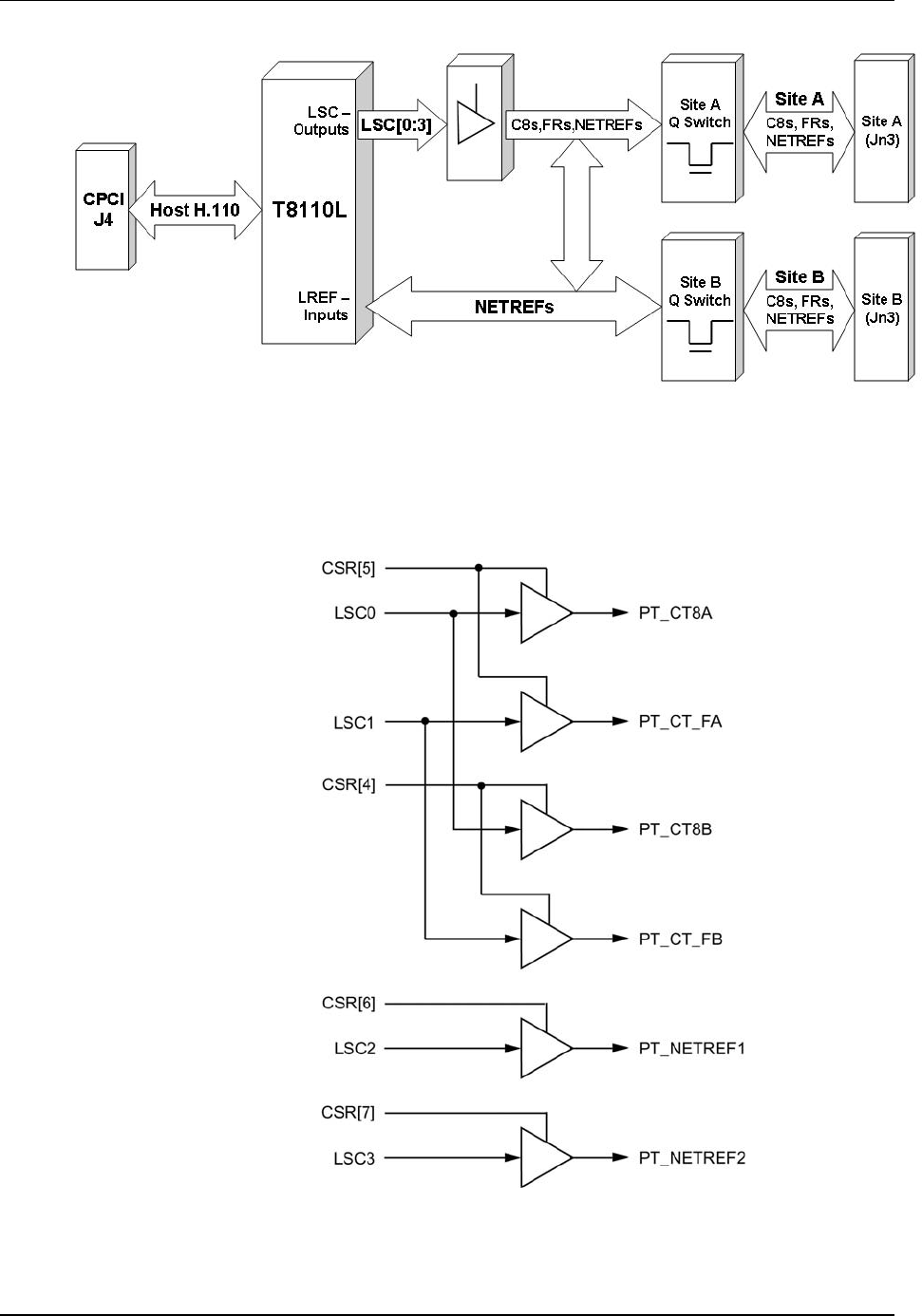

Figure 10. Local CT Bus Clocking Block Diagram

Control for the local “A” and “B” bus drivers is provided by bits 4, 5, 6, and 7 in the

Clock Select Register (CSR). Refer to Section 4.2.1 for further details. Figure 11

shows the implementation.

Figure 11. Local CT Bus Clock Generation

October 10, 2006 Copyright 2006, SBE, Inc. Page 26