HighWire HW400c/2 User Reference Guide Rev 1.0

4.2.25 SPI Error and Status Register (SESR)

The SPI Error Register is a Read Only register. SBSY clears when the previous

operation is completed, and the SPIFER, RACKER, and BYTER error flags clear

when the next operation is started.

PIFER, RACKER and BYTER are valid after SBSY=0 (Interface Ready), but are

T

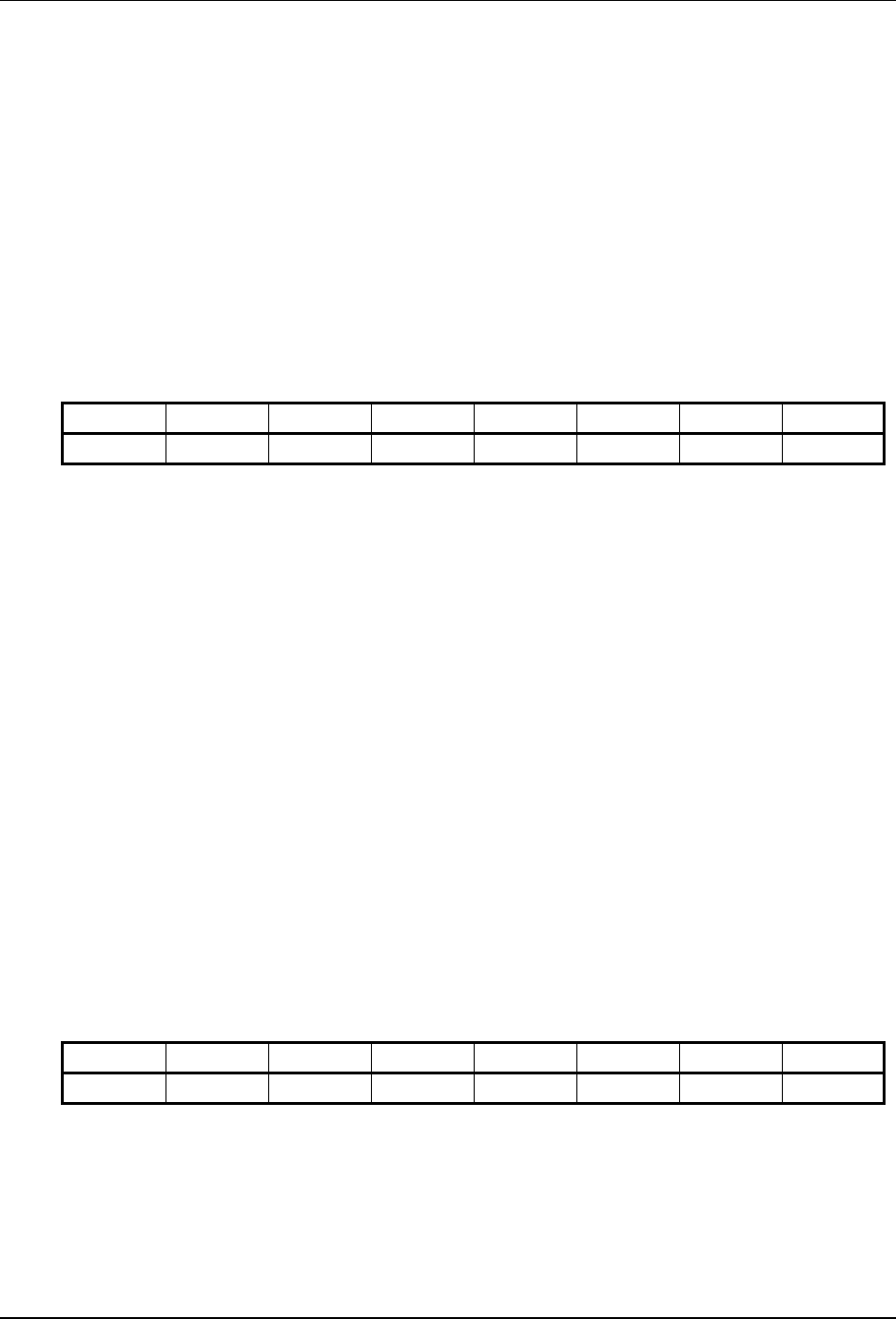

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

SBSY can be polled immediately after writing to the RBC or WBC registers.

S

cleared when writing to the RBC or WBC registers for the next operation.

able 55. SPI Error and Status Register (SESR) Offset Address 0x1F

Reser BSY ved Reserved Reserved Reserved BYTER RACKER SPIFER S

SB SPI Interface ready for re e ope

SPI Interface busy; oper rogr

PI R = 0 SPIF Check passed

= 1 SPIF Check failed; no operation performed

Byte count was OK

4.2.26 EEPROM ddress (EAR)

he EEPRO Addres Register is a Read/Write register. It is used for selecting the

16- ord) M.

ster (EAR) Offset Address 0x28

Bit 7

SY = 0 ad/writ ration

= 1 ation in p ess

S FE

= 0 RACK Check passed RACKER

= 1 RACK Check failed; no operation performed

= 0

BYTER

= 1 Byte count was zero; no operation performed

A Register

T M s

desired ( bit w address when accessing the serial EEPRO

Table 56. EEPROM Address Regi

Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

EAR7 EAR6 EAR5 EAR4 EAR3 EAR2 EAR1 EAR0

EAR[7:0] = 0x00 – 0xFF (Word Address)

October 10, 2006 Copyright 2006, SBE, Inc. Page 61