HighWire HW400c/2 User Reference Guide Rev 1.0

4.2.4 Memory Option Register (MOR)

T

The Memory Option Register (MOR) is a Read-Only register. This register reports

the presence and size of the M-Systems Disk on Chip device.

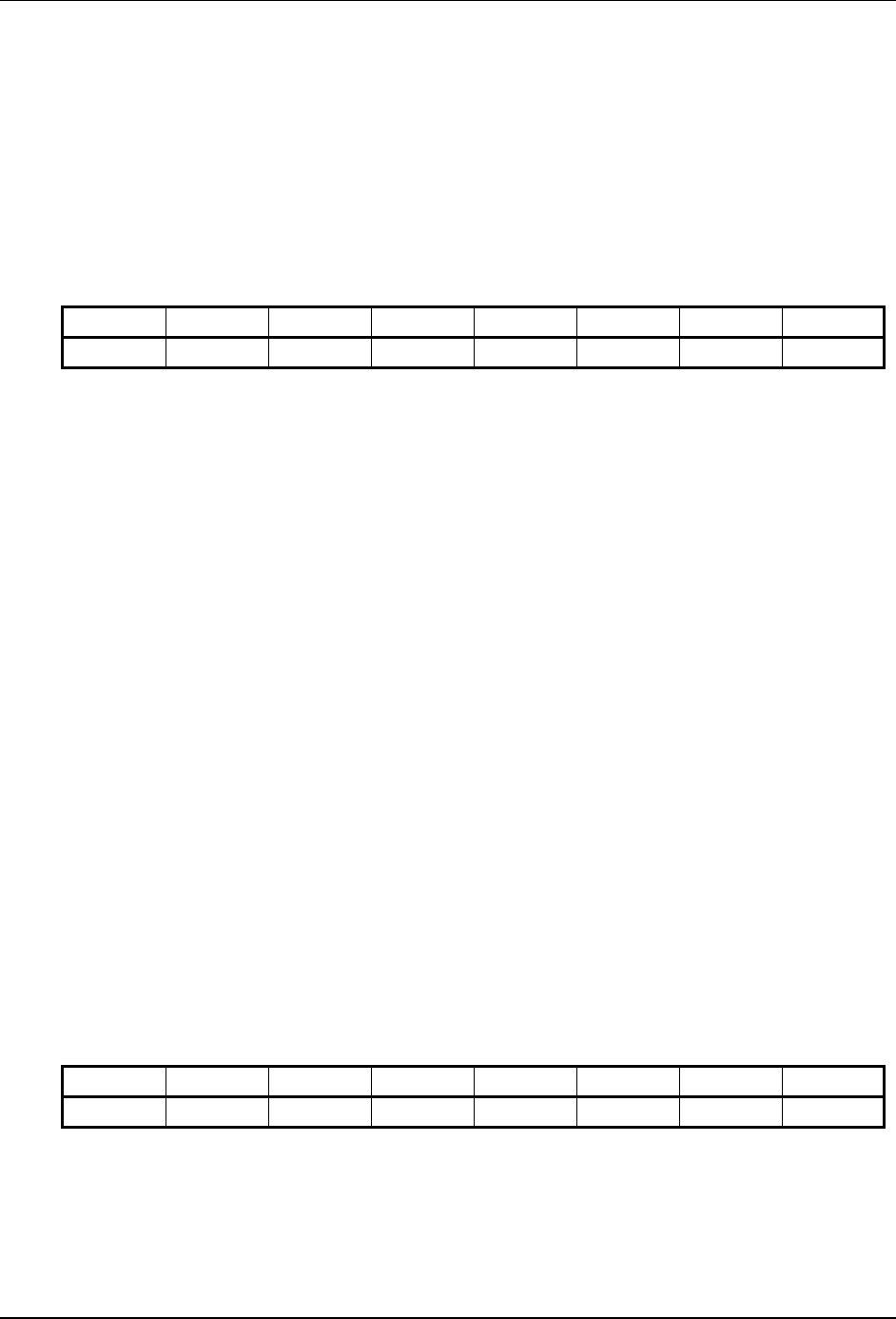

able 33. Memory Option Register (MOR) Offset Address 0x07

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

DOC3 DOC2 DOC1 DOC0 Reserved Reserved Reserved Reserved

DOC3 = 0 Disk-on-Chip de-populated

OC[2:0] = 000 Disk-on-Chip Size is 64 MB

= 001 Disk-on-Chip Size is 128 MB (default)

Disk-on-Chip Size is 256 MB

Disk-on-Chip Size is 512 MB

4.2.5 Geographi

he Geographic Addressing Register (GAR) is a Read Only register. This register

sh pactPCI

backplane connectors J2 and/or J4.

Ge ical A sing B ine a al loc slot) i ompa

b . T s o 4 s ide e r bo

connectors mirroring the bit that in s onfigur ns (e.g. lane

r a non H.110 backplane) one or the other connector may not be present. For a

of th grap MG 2.0 and PICMG 2.5.

T g d 08

Bit 7 Bit 6 Bit 0

= 1 Disk-on-Chip populated (default)

D

= 010

= 011

= 100 Disk-on-Chip Size is 1 GB

= 101 Disk-on-Chip Size is 2 GB

= 110 Disk-on-Chip Size is 4 GB

= 111 Disk-on-Chip Size is 8 GB

c Addressing Register (GAR)

T

ows the value of the Geographic Address Bits as read from the Com

ograph ddres its def physic ation ( n the C ctPCI

ackplane he setting f J2 and J hould be ntical. Th eason for th

s is ome c atio a non-PCI backp

o

definition e Geo hic Address Bits, see PIC

able 34. Geo raphic A dressing Register (CSR) Offset Address 0x

Bit 5 Bit 4 Bit 3 Bit 2 Bit 1

Reserved Re d GA2 GA1 GA0 Reserved serve GA4 GA3

GA[4:0] = Geographic Address Bits as read from CompactPCI J2

onnectors and/or J4 (backplane) c

October 10, 2006 Copyright 2006, SBE, Inc. Page 50