HighWire HW400c/2 User Reference Guide Rev 1.0

4.2.12 Hardware Revision Register (HRR)

The Hardware Revision Register (HRR) is a Read-Only register. It contains the

current major and minor (optional) hardware revision for the board.

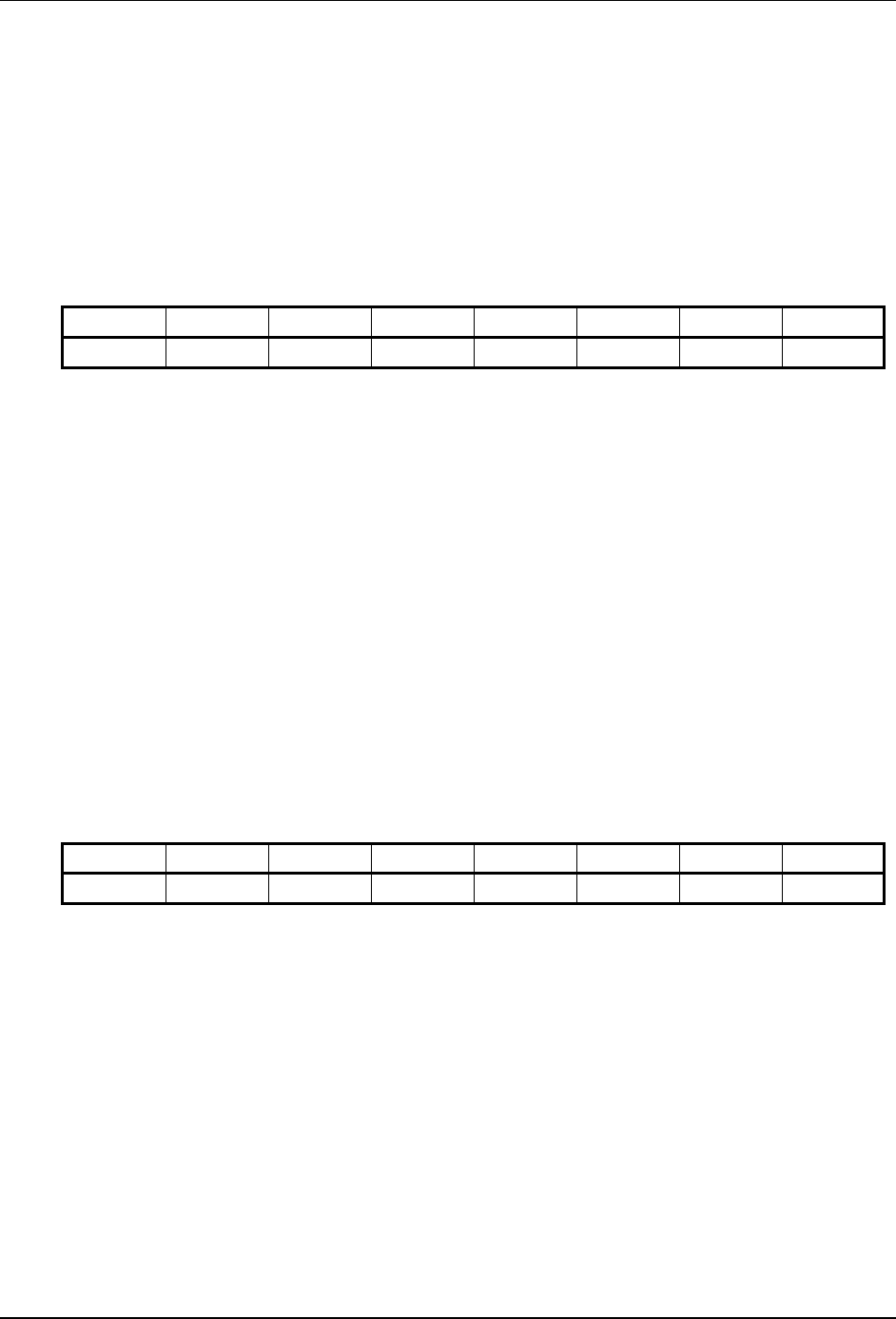

Table 41. Hardware Revision Register (HRR) Offset Address

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

HRR7 HRR6 HRR5 HRR4 HRR3 HRR2 HRR1 HRR0

RR[7:4] = xxxx HW400c/2 Major Revision

4.2.13 PLL Conf uration Re r A

nfi on R s the

ttings for the PLL ftware

etermine the C pera ase refer to either the MPC7447A or

PC7448 Hard Spe ocuments, in the PLL Configuration section, for

table of all po valu

Table 42. PLL Configuration Register A (PLLA) Offset Address 0x12

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

H

HRR[3:0] = yyyy HW400c/2 Minor Revision

ig giste (PLLA)

The PLL Co gurati egister A (PLLA) is a Read-Only register. It contain

. Reading this register (along with PLLB) can help so

ncy. Ple

se CPU

d PU o ting freque

M ware

ssible

cifications d

es. a

Reserved Reserved CPLL5 CPLL4 CPLL3 CPLL2 CPLL1 CPLL0

CPLL[5:0] = 0x0B Default setting for HW400c/2 Standard Version

(CPU core clock is 1.0 GHz when system bus clock is

166 MHz)

October 10, 2006 Copyright 2006, SBE, Inc. Page 54