HighWire HW400c/2 User Reference Guide Rev 1.0

Table 23. Voltage Monitor A/D Port Assignments for IPMI

Supply Voltage Monitor A/D Port

5-Volt A2D1

3.3-Volt A2D2

1.1-Volt (CPU core) A2D3

1.5-Volt (System controller core) A2D4

2.5-Volt (SDRAM) A2D5

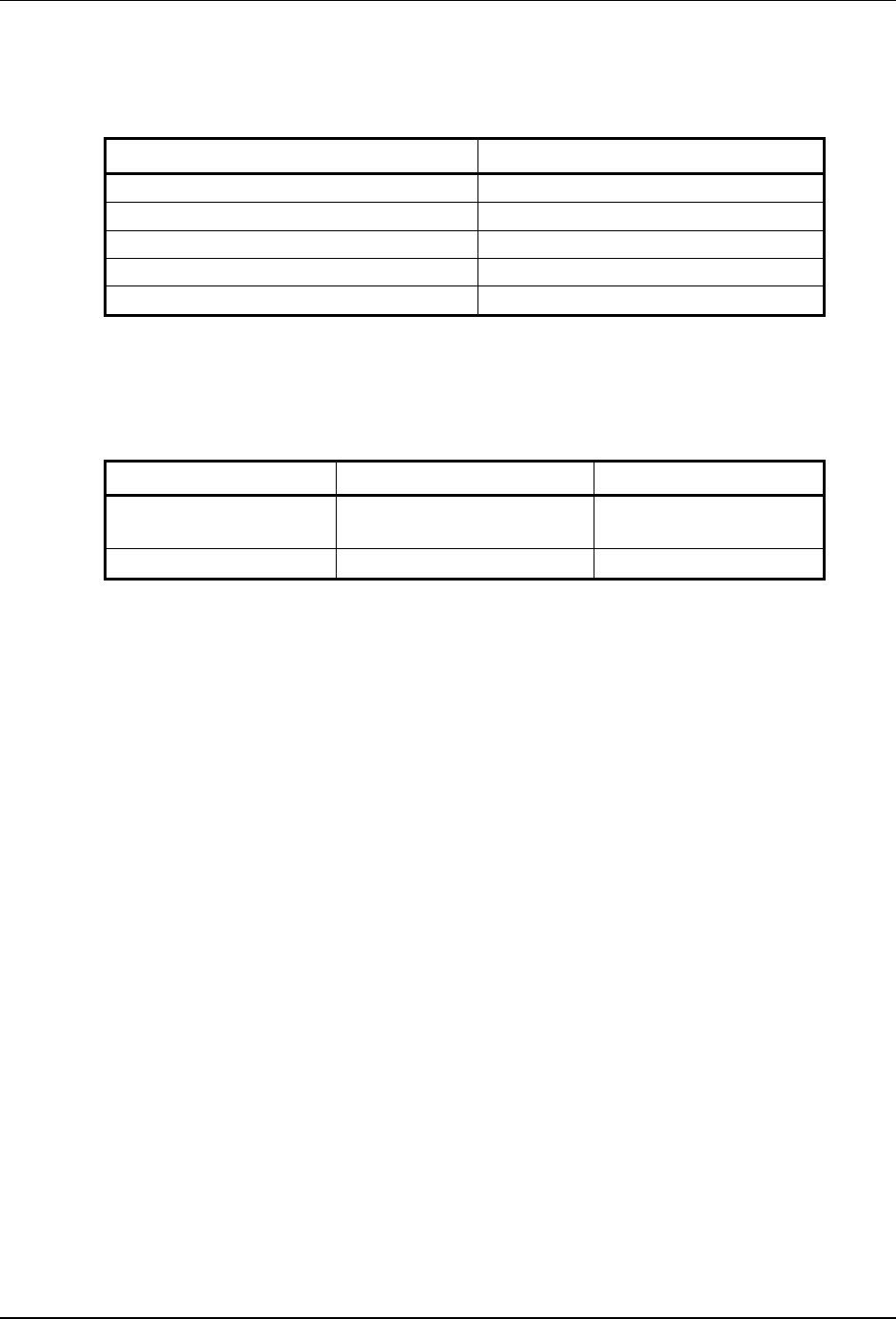

Table 24. HW400c/2 Temperature Sensor Locations

Location I

2

C Port 1 Address

Device

TS0 (U84)

Controller

0

MV64462 System

TS1 (U83) CPU Internal Temperature 1

3.6.3 Hot Swap

he IPMI controller has the capability to read the state of the hot swap ejector switch,

3.6.4 Blue (Hot Swap) LED Control

3.6.5 Boot Status Monitor

There are four (4) register bits in the CPLD reserved for indicating the boot status

le T ted IO port as

shown in Tab power-up default va r

valu r SBE us

Ejector Latch Detection

T

otherwise known as the L_STAT signal. This signal is connected to a GPIO pin on

the Zircon PM (see Table 22). L_STAT = 0 indicates the ejector latch is closed,

L_STAT = 1 indicates it is open, and that the board is about to be removed

The IPMI controller has the capability to turn on the Blue Front Panel LED. A GPIO

pin on the Zircon PM is connected through the CPLD to the LED (see Table 22).

vel from the processor. hese bits are connec

lue of the

to the Zircon PM GP

se bits is “0000.” All othele 22. The

es are reserved fo e.

October 10, 2006 Copyright 2006, SBE, Inc. Page 41