137/163

uPSD3212A, uPSD3212C, uPSD3212CV

Note: 1. I

PD

(Power-down Mode) is measured with:

2. XTAL1=V

SS

; XTAL2=not connected; RESET=V

CC

; Port 0 =V

CC

; all other pins are disconnected. PLD not in Turbo Mode.

3. I

CC_CPU

(active mode) is measured with:

4. XTAL1 driven with t

CLCH

, t

CHCL

= 5ns, V

IL

= V

SS

+0.5V, V

IH

= V

CC

– 0.5V, XTAL2 = not connected; RESET=V

SS

; Port 0=V

CC

; all

other pins are disconnected. I

CC

would be slightly higher if a crystal oscillator is used (approximately 1mA).

5. I

CC_CPU

(Idle Mode) is measured with:

6. XTAL1 driven with t

CLCH

, t

CHCL

= 5ns, V

IL

= V

SS

+0.5V, V

IH

= V

CC

– 0.5V, XTAL2 = not connected; Port 0 = V

CC

;

7. RESET

=V

CC

; all other pins are disconnected.

8. See Figure 68., page 128 for the PLD current calculation.

9. I/O current = 0mA, all I/O pins are disconnected.

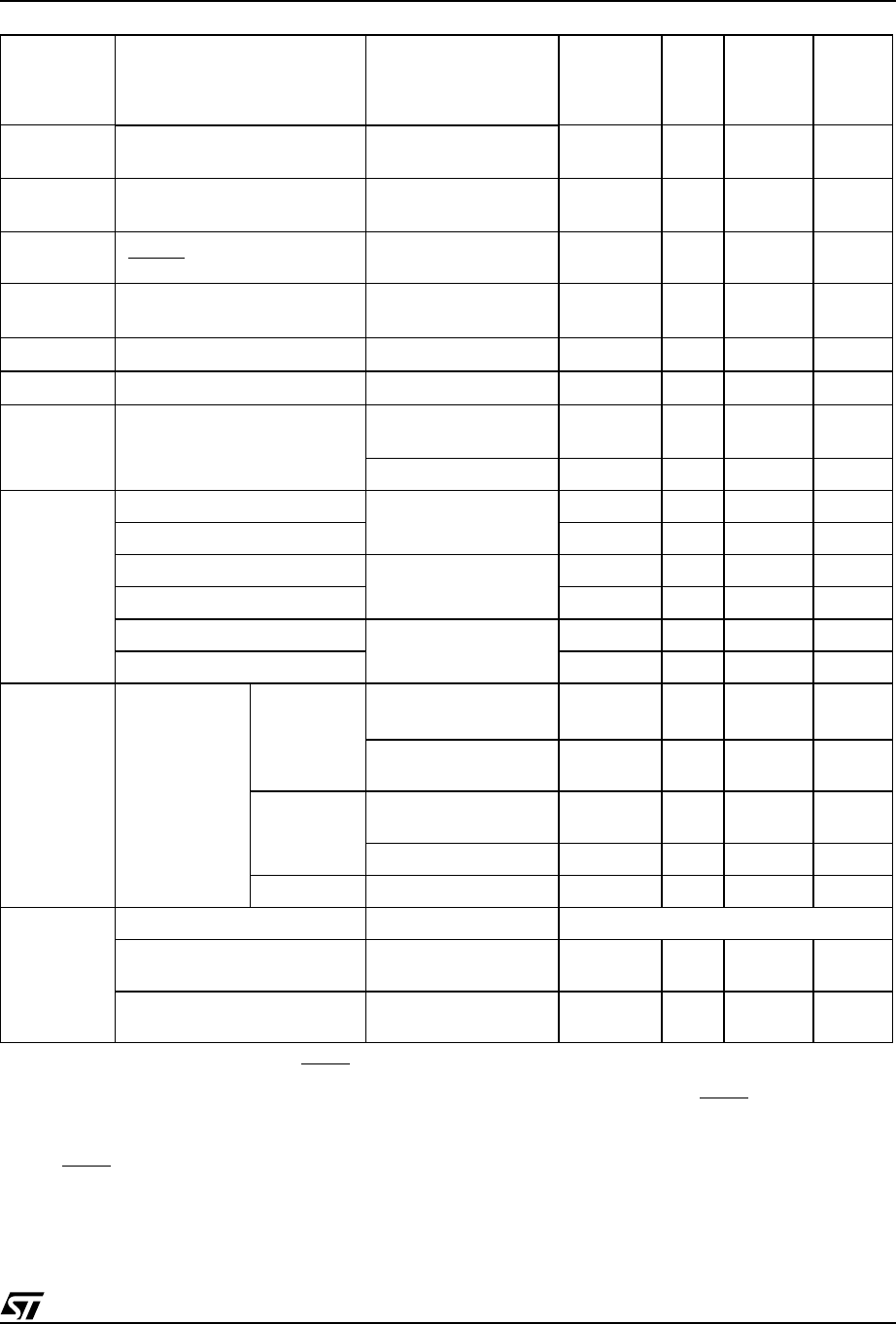

I

STBY

SRAM (PSD) Standby Current

(V

STBY

input)

V

CC

= 0V

0.5 1 µA

I

IDLE

SRAM (PSD) Idle Current

(V

STBY

input)

V

CC

> V

STBY

–0.1 0.1 µA

I

RST

Reset Pin Pull-up Current

(RESET

)

V

IN

= V

SS

–10 –55 µA

I

FR

XTAL Feedback Resistor

Current (XTAL1)

XTAL1 = V

CC

XTAL2 = V

SS

–20 –50 µA

I

LI

Input Leakage Current

V

SS

< V

IN

< V

CC

–1 1 µA

I

LO

Output Leakage Current

0.45 < V

OUT

< V

CC

–10 10 µA

I

PD

(1)

Power-down Mode

V

CC

= 5.5V

LVD logic disabled

250 µA

LVD logic enabled 380 µA

I

CC_CPU

(2,3,5)

Active (12MHz)

V

CC

= 5V

20 30 mA

Idle (12MHz) 8 10 mA

Active (24MHz)

V

CC

= 5V

30 38 mA

Idle (24MHz) 15 20 mA

Active (40MHz)

V

CC

= 5V

40 62 mA

Idle (40MHz) 20 30 mA

I

CC_PSD

(DC)

(5)

Operating

Supply Current

PLD Only

PLD_TURBO = Off,

f = 0MHz

(4)

0

µA/PT

(5)

PLD_TURBO = On,

f = 0MHz

400 700 µA/PT

Flash

memory

During Flash memory

WRITE/Erase Only

15 30 mA

Read only, f = 0MHz 0 0 mA

SRAM f = 0MHz 0 0 mA

I

CC_PSD

(AC)

(5)

PLD AC Base Note 4

Flash memory AC Adder 2.5 3.5

mA/

MHz

SRAM AC Adder 1.5 3.0

mA/

MHz

Symbol Parameter

Test Condition

(in addition to those

in Table

109., page 133)

Min. Typ. Max. Unit