143/163

uPSD3212A, uPSD3212C, uPSD3212CV

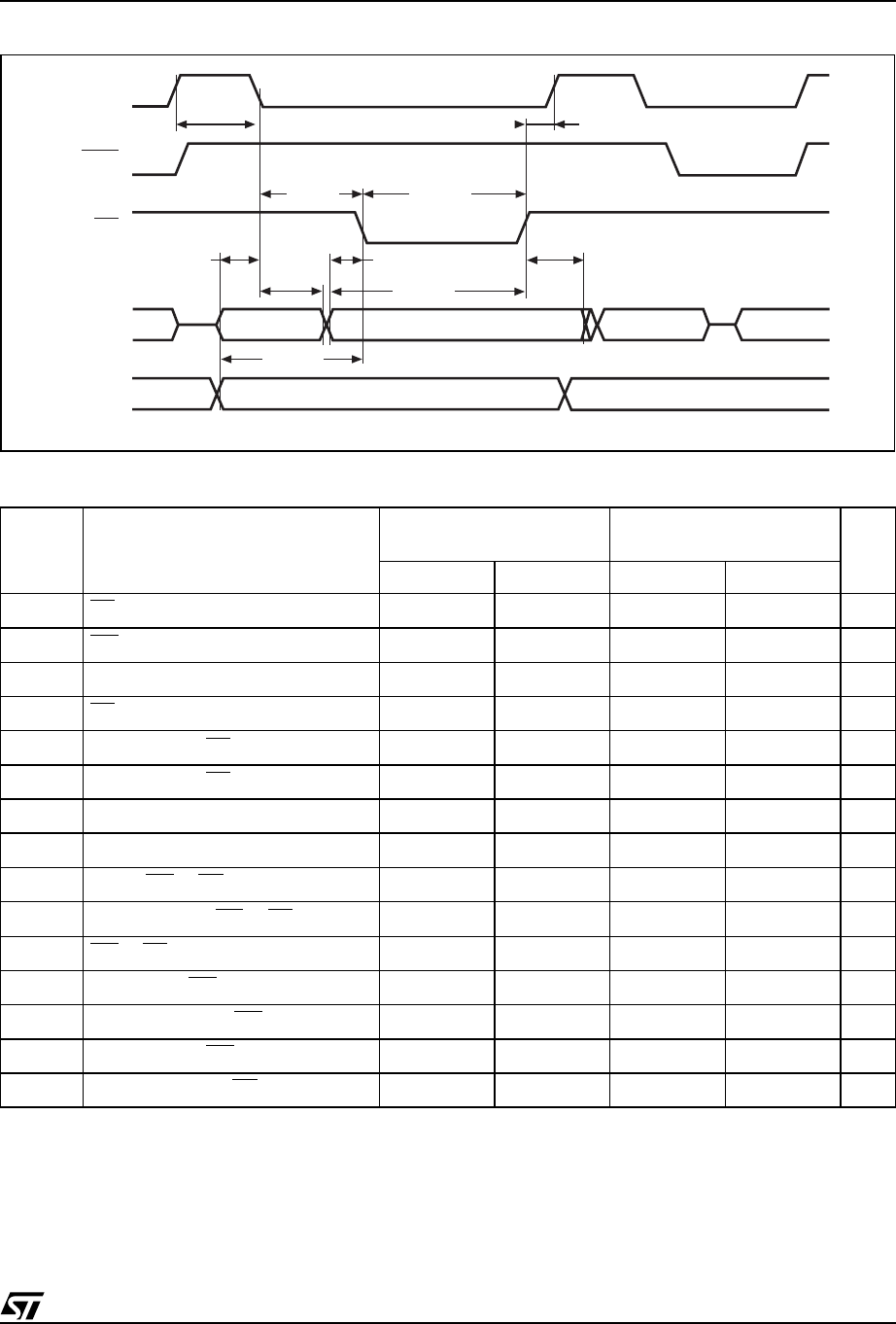

Figure 73. External Data Memory WRITE Cycle

Table 120. External Data Memory AC Characteristics (with the 5V MCU Module)

Note: 1. Conditions (in addition to those in Table 109., page 133, V

CC

= 4.5 to 5.5V): V

SS

= 0V; C

L

for Port 0, ALE and PSEN output is 100pF;

C

L

for other outputs is 80pF

Symbol

Parameter

(1)

40MHz Oscillator

Variable Oscillator

1/t

CLCL

= 24 to 40MHz

Unit

Min Max Min Max

t

RLRH

RD pulse width 120

6t

CLCL

– 30

ns

t

WLWH

WR pulse width 120

6t

CLCL

– 30

ns

t

LLAX2

Address hold after ALE 10

t

CLCL

– 15

ns

t

RHDX

RD to valid data in 75

5t

CLCL

– 50

ns

t

RHDX

Data hold after RD 00ns

t

RHDZ

Data float after RD 38

2t

CLCL

– 12

ns

t

LLDV

ALE to valid data in 150

8t

CLCL

– 50

ns

t

AVDV

Address to valid data in 150

9t

CLCL

– 75

ns

t

LLWL

ALE to WR or RD 60 90

3t

CLCL

– 15 t

CLCL

+ 15

ns

t

AVWL

Address valid to WR or RD 70

4t

CLCL

– 30

ns

t

WHLH

WR or RD High to ALE High 10 40

t

CLCL

– 15 t

CLCL

+ 15

ns

t

QVWX

Data valid to WR transition 5

t

CLCL

– 20

ns

t

QVWH

Data set up before WR 125

7t

CLCL

– 50

ns

t

WHQX

Data hold after WR 5

t

CLCL

– 20

ns

t

RLAZ

Address float after RD 00ns

PORT 2

PORT 0

ALE

WR

PSEN

P2.0 to P2.3 or A8-A11 from DPH A8-A11 from PCH

tQVWX

tLLWL

tWLWH

tAVLL

tLHLL

tQVWH

DATA OUT A0-A7 from PCL INSTR IN

A0-A7 from

RI or DPL

tLLAX

tAVWL

tWHQX

tWHLH

AI07089