uPSD3212A, uPSD3212C, uPSD3212CV

154/163

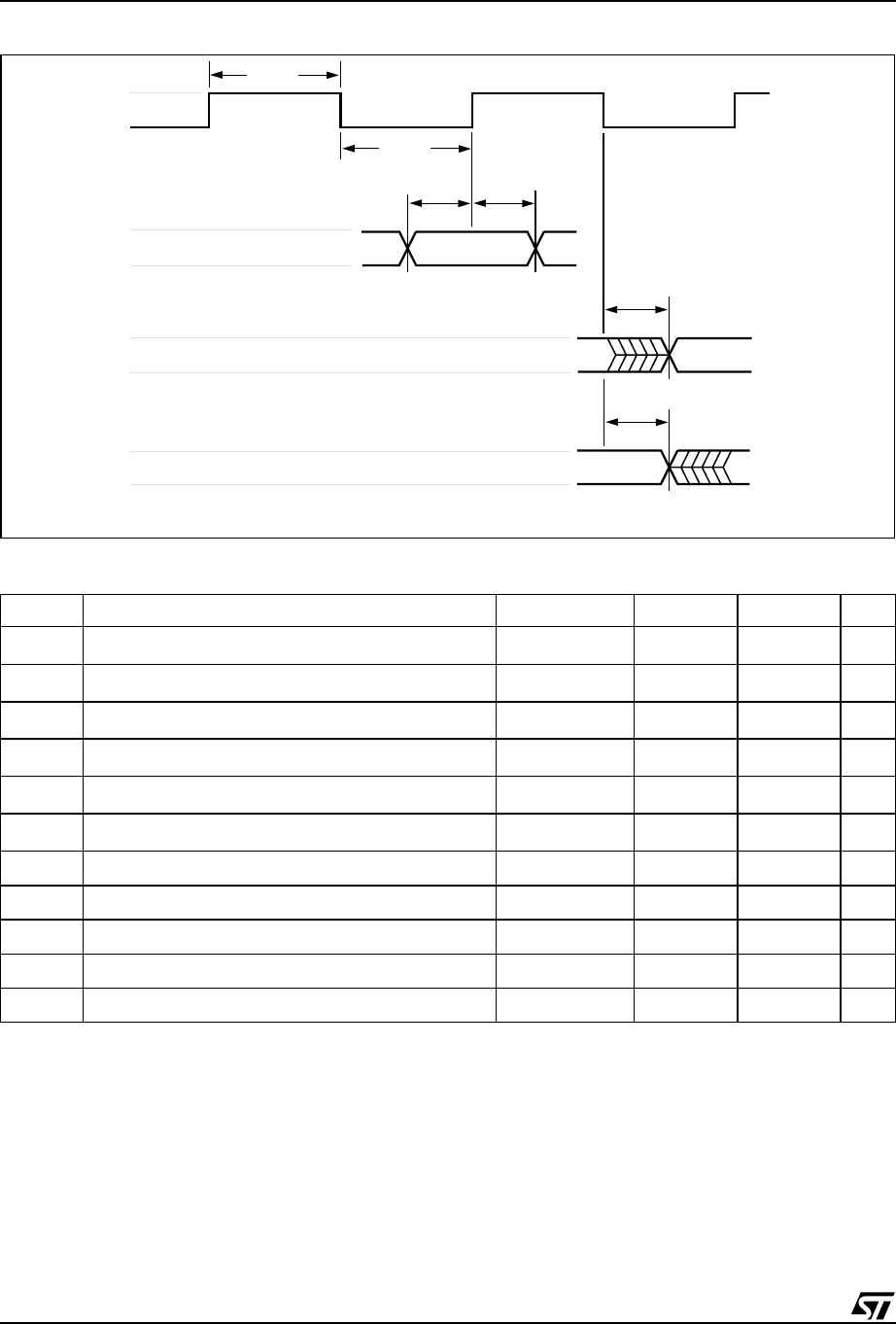

Figure 82. ISC Timing

Table 141. ISC Timing (5V Devices)

Note: 1. For non-PLD Programming, Erase or in ISC By-pass Mode.

2. For Program or Erase PLD only.

Symbol Parameter Conditions Min Max Unit

t

ISCCF

Clock (TCK, PC1) Frequency (except for PLD)

(Note

1)

20 MHz

t

ISCCH

Clock (TCK, PC1) High Time (except for PLD)

(Note

1)

23 ns

t

ISCCL

Clock (TCK, PC1) Low Time (except for PLD)

(Note

1)

23 ns

t

ISCCFP

Clock (TCK, PC1) Frequency (PLD only)

(Note

2)

2MHz

t

ISCCHP

Clock (TCK, PC1) High Time (PLD only)

(Note

2)

240 ns

t

ISCCLP

Clock (TCK, PC1) Low Time (PLD only)

(Note

2)

240 ns

t

ISCPSU

ISC Port Set Up Time 7 ns

t

ISCPH

ISC Port Hold Up Time 5 ns

t

ISCPCO

ISC Port Clock to Output 21 ns

t

ISCPZV

ISC Port High-Impedance to Valid Output 21 ns

t

ISCPVZ

ISC Port Valid Output to High-Impedance 21 ns

ISCCH

TCK

TDI/TMS

ISC OUTPUTS/TDO

ISC OUTPUTS/TDO

t

ISCCL

t

ISCPH

t

ISCPSU

t

ISCPVZ

t

ISCPZV

t

ISCPCO

t

AI02865