uPSD3212A, uPSD3212C, uPSD3212CV

52/163

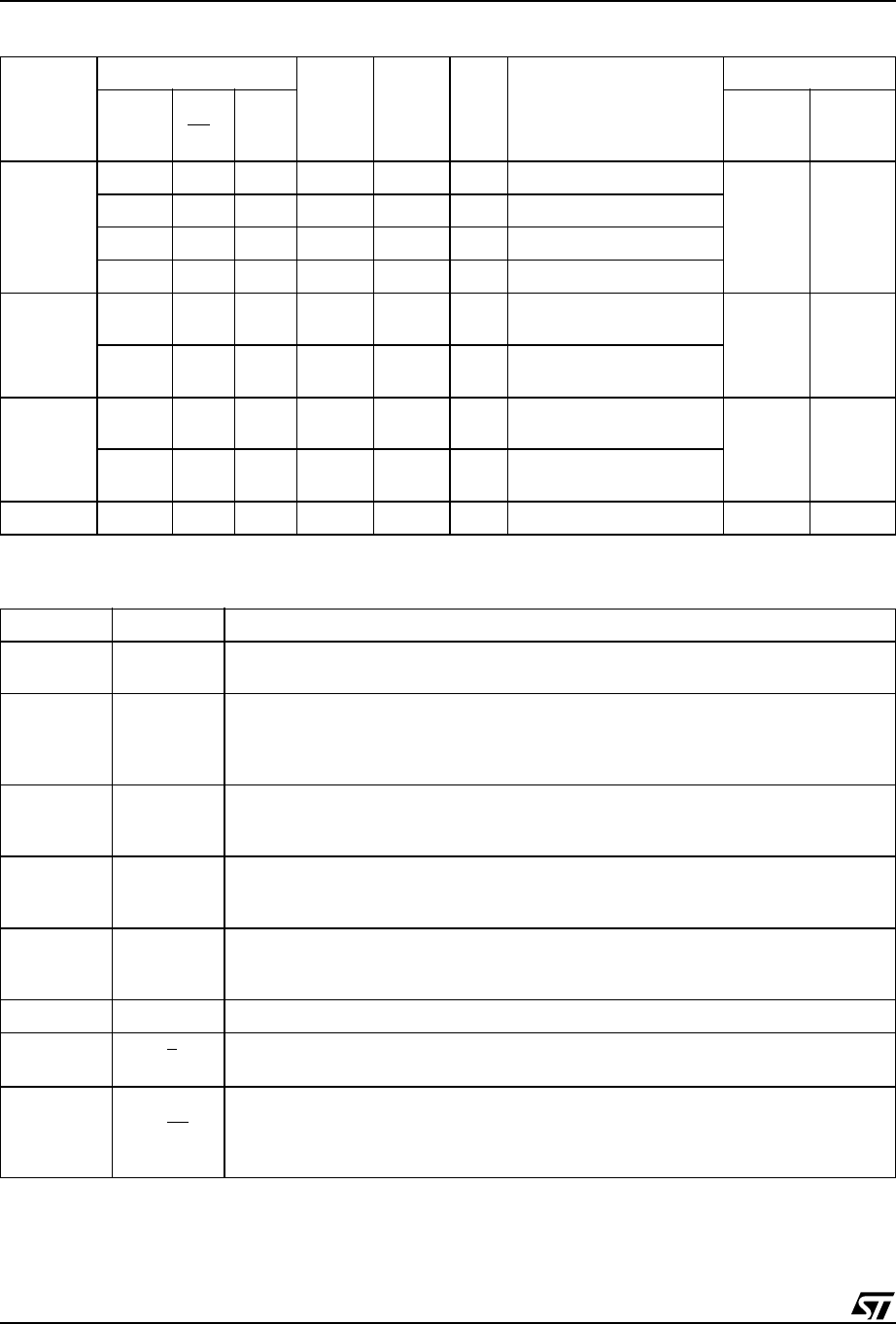

Table 41. Timer/Counter 2 Operating Modes

Note: ↓ = falling edge

Table 42. Description of the T2CON Bits

Note: 1. The RCLK1 and TCLK1 Bits in the PCON Register control UART 2, and have the same function as RCLK and TCLK.

Mode

T2CON

T2MOD

DECN

T2CON

EXEN

P1.1

T2EX

Remarks

Input Clock

RxCLK

or

TxCLK

CP/

RL

2

TR2 Internal

External

(P1.0/T2)

16-bit

Auto-

reload

0 0 1 0 0 x reload upon overflow

f

OSC

/12

MAX

f

OSC

/24

0010 1↓ reload trigger (falling edge)

0 0 1 1 x 0 Down counting

0 0 1 1 x 1 Up counting

16-bit

Capture

011x 0x

16-bit Timer/Counter

(only up counting)

f

OSC

/12

MAX

f

OSC

/24

011x 1↓

Capture (TH1,TL2) →

(RCAP2H,RCAP2L)

Baud Rate

Generator

1x1x 0x

No Overflow Interrupt

Request (TF2)

f

OSC

/12

MAX

f

OSC

/24

1x1x 1↓

Extra External Interrupt

(Timer 2)

Off x x 0 x x x Timer 2 stops — —

Bit Symbol Function

7TF2

Timer 2 Overflow Flag. Set by a Timer 2 overflow, and must be cleared by software. TF2

will not be set when either (RCLK, RCLK1)=1 or (TCLK, TCLK)=1

6EXF2

Timer 2 External Flag set when either a capture or reload is caused by a negative

transition on T2EX and EXEN2=1. When Timer 2 Interrupt is enabled, EXF2=1 will

cause the CPU to vector to the Timer 2 Interrupt routine. EXF2 must be cleared by

software

5

RCLK

(1)

Receive Clock Flag (UART 1). When set, causes the serial port to use Timer 2 overflow

pulses for its receive clock in Modes 1 and 3. TCLK=0 causes Timer 1 overflow to be

used for the receive clock

4

TCLK

(1)

Transmit Clock Flag (UART 1). When set, causes the serial port to use Timer 2 overflow

pulses for its transmit clock in Modes 1 and 3. TCLK=0 causes Timer 1 overflow to be

used for the transmit clock

3 EXEN2

Timer 2 External Enable Flag. When set, allows a capture or reload to occur as a result

of a negative transition on T2EX if Timer 2 is not being used to clock the serial port.

EXEN2=0 causes Time 2 to ignore events at T2EX

2 TR2 Start/stop control for Timer 2. A logic 1 starts the timer

1C/T

2

Timer or Counter Select for Timer 2. Cleared for timer operation (input from internal

system clock, t

CPU

); set for external event counter operation (negative edge triggered)

0CP/RL

2

Capture/Reload Flag. When set, capture will occur on negative transition of T2EX if

EXEN2=1. When cleared, auto-reload will occur either with TImer 2 overflows, or

negative transitions of T2EX when EXEN2=1. When either (RCLK, RCLK1)=1 or (TCLK,

TCLK)=1, this bit is ignored, and timer is forced to auto-reload on Timer 2 overflow