uPSD3212A, uPSD3212C, uPSD3212CV

152/163

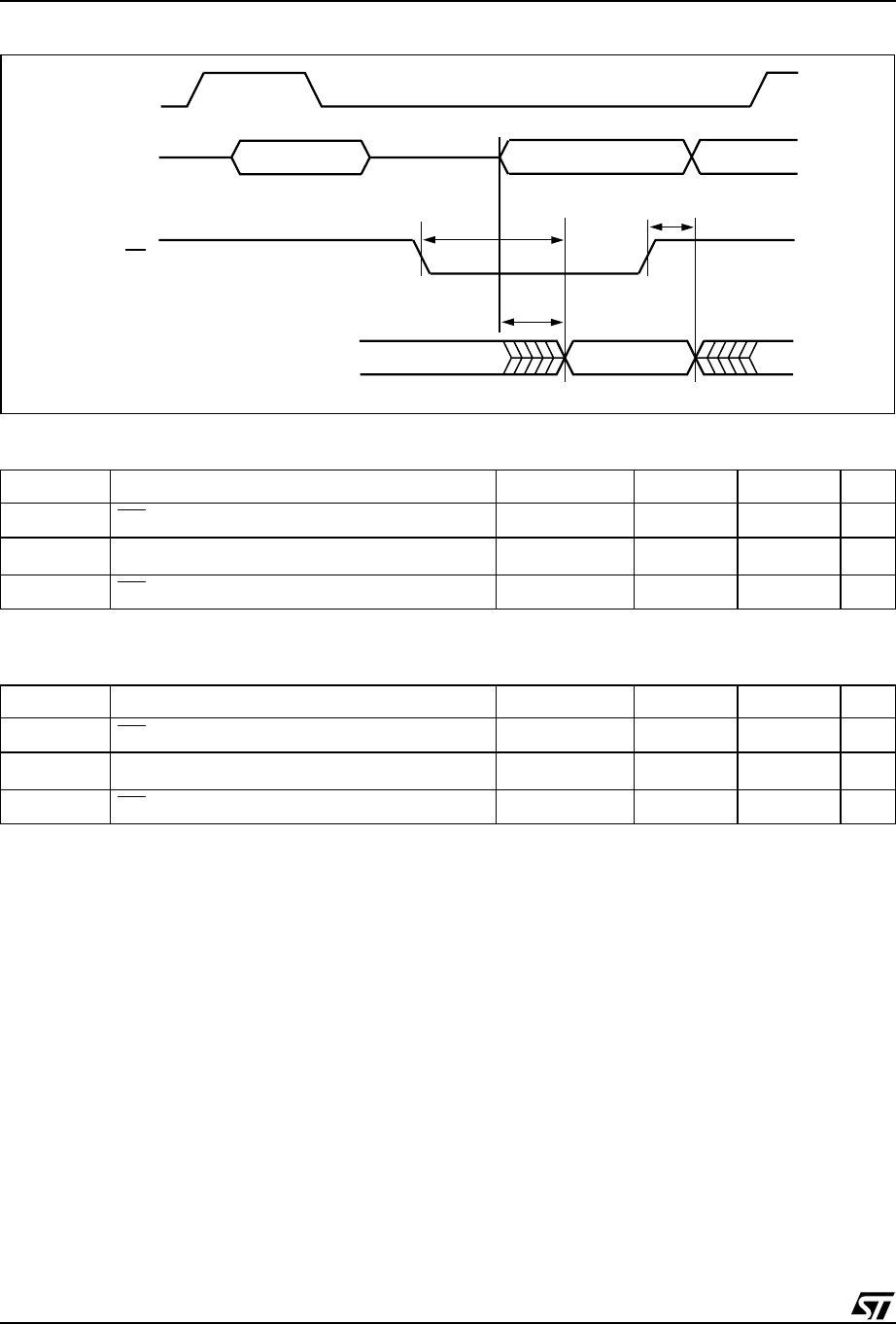

Figure 80. Peripheral I/O WRITE Timing

Table 135. Port A Peripheral Data Mode WRITE Timing (5V Devices)

Note: 1. Data stable on Port 0 pins to data on Port A.

Table 136. Port A Peripheral Data Mode WRITE Timing (3V Devices)

Note: 1. Data stable on Port 0 pins to data on Port A.

Symbol Parameter Conditions Min Max Unit

t

WLQV–PA

WR to Data Propagation Delay 25 ns

t

DVQV–PA

Data to Port A Data Propagation Delay

(Note

1)

22 ns

t

WHQZ–PA

WR Invalid to Port A Tri-state 20 ns

Symbol Parameter Conditions Min Max Unit

t

WLQV–PA

WR to Data Propagation Delay 42 ns

t

DVQV–PA

Data to Port A Data Propagation Delay

(Note

1)

38 ns

t

WHQZ–PA

WR Invalid to Port A Tri-state 33 ns

tDVQV (PA)

tWLQV (PA)

tWHQZ (PA)

ADDRESS DATA OUT

A/D BUS

WR

PORT A

DATA OUT

ALE

AI06611