147/163

uPSD3212A, uPSD3212C, uPSD3212CV

Table 126. CPLD Macrocell Synchronous Clock Mode Timing (3V Devices)

Note: 1. Fast Slew Rate output available on PA3-PA0, PB3-PB0, and PD2-PD1. Decrement times by given amount.

2. CLKIN (PD1) t

CLCL

= t

CH

+ t

CL

.

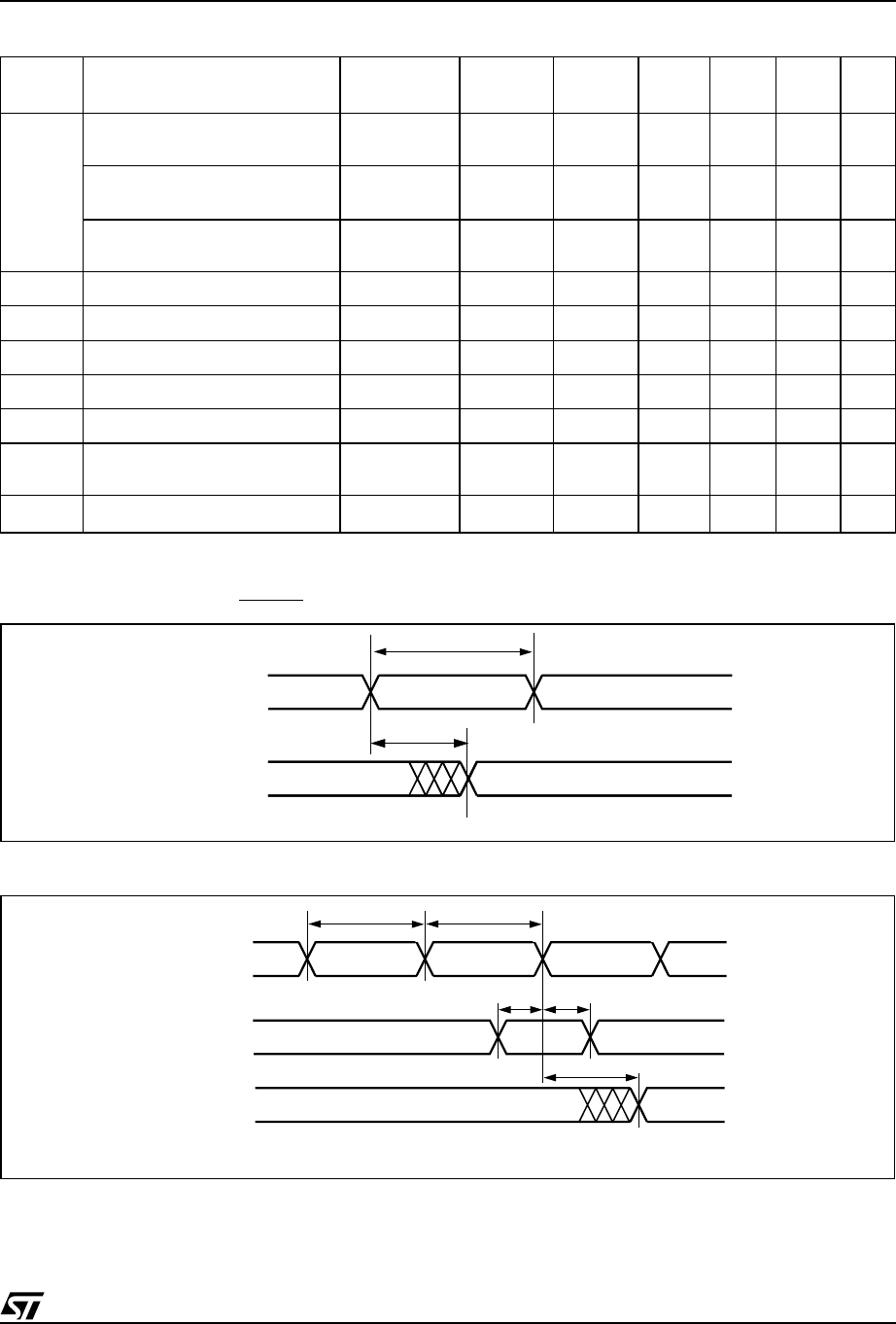

Figure 76. Asynchronous RESET / Preset

Figure 77. Asynchronous Clock Mode Timing (Product Term Clock)

Symbol Parameter Conditions Min Max

PT

Aloc

Turbo

Off

Slew

rate

(1)

Unit

f

MAX

Maximum Frequency

External Feedback

1/(t

S

+t

CO

)

22.2 MHz

Maximum Frequency

Internal Feedback (f

CNT

)

1/(t

S

+t

CO

–10)

28.5 MHz

Maximum Frequency

Pipelined Data

1/(t

CH

+t

CL

)

40.0 MHz

t

S

Input Setup Time 20 + 4 + 20 ns

t

H

Input Hold Time 0 ns

t

CH

Clock High Time Clock Input 15 ns

t

CL

Clock Low Time Clock Input 10 ns

t

CO

Clock to Output Delay Clock Input 25 – 6 ns

t

ARD

CPLD Array Delay

Any

macrocell

25 + 4 ns

t

MIN

Minimum Clock Period

(2)

t

CH

+t

CL

25 ns

tARP

REGISTER

OUTPUT

tARPW

RESET/PRESET

INPUT

AI02864

tCHA

tCLA

tCOA

tHAtSA

CLOCK

INPUT

REGISTERED

OUTPUT

AI02859