69/163

uPSD3212A, uPSD3212C, uPSD3212CV

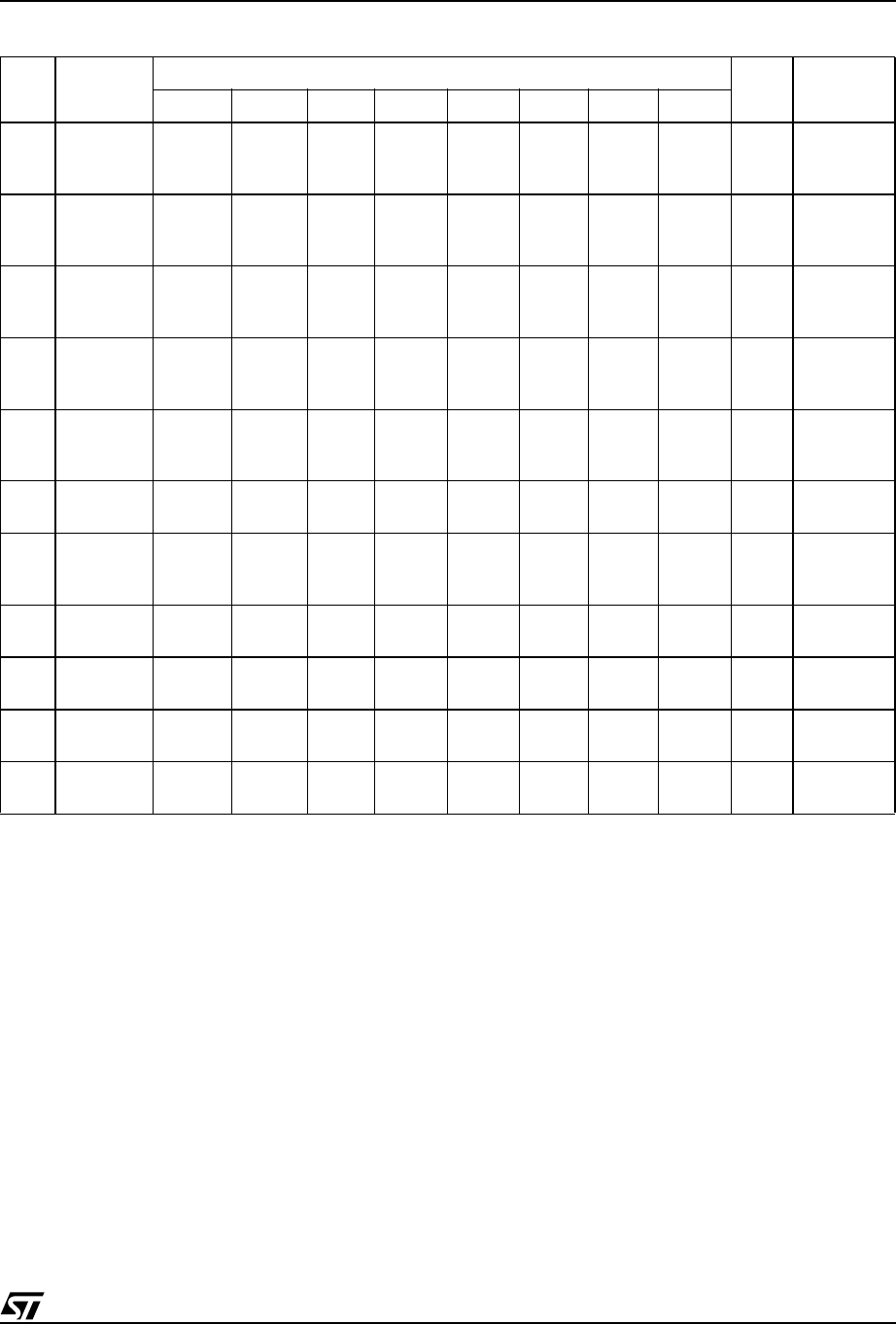

Table 49. PWM SFR Memory Map

PWMCON Register Bit Definition:

– PWML = PWM 0-3 polarity control

– PWMP = PWM 4 polarity control

– PWME = PWM enable (0 = disabled, 1=

enabled)

– CFG3..CFG0 = PWM 0-3 Output (0 = Open

Drain; 1 = Push-Pull)

– CFG4 = PWM 4 Output (0 = Open Drain; 1 =

Push-Pull)

SFR

Addr

Reg Name

Bit Register Name

Reset

Value

Comment

s

76543210

A1 PWMCON PWML PWMP PWME CFG4 CFG3 CFG2 CFG1 CFG0 00

PWM

Control

Polarity

A2 PWM0 00

PWM0

Output

Duty Cycle

A3 PWM1 00

PWM1

Output

Duty Cycle

A4 PWM2 00

PWM2

Output

Duty Cycle

A5 PWM3 00

PWM3

Output

Duty Cycle

AA PWM4P 00

PWM 4

Period

AB PWM4W 00

PWM 4

Pulse

Width

B1 PSCL0L 00

Prescaler 0

Low (8-bit)

B2 PSCL0H 00

Prescaler 0

High (8-bit)

B3 PSCL1L 00

Prescaler 1

Low (8-bit)

B4 PSCL1H 00

Prescaler 1

High (8-bit)