www.ti.com

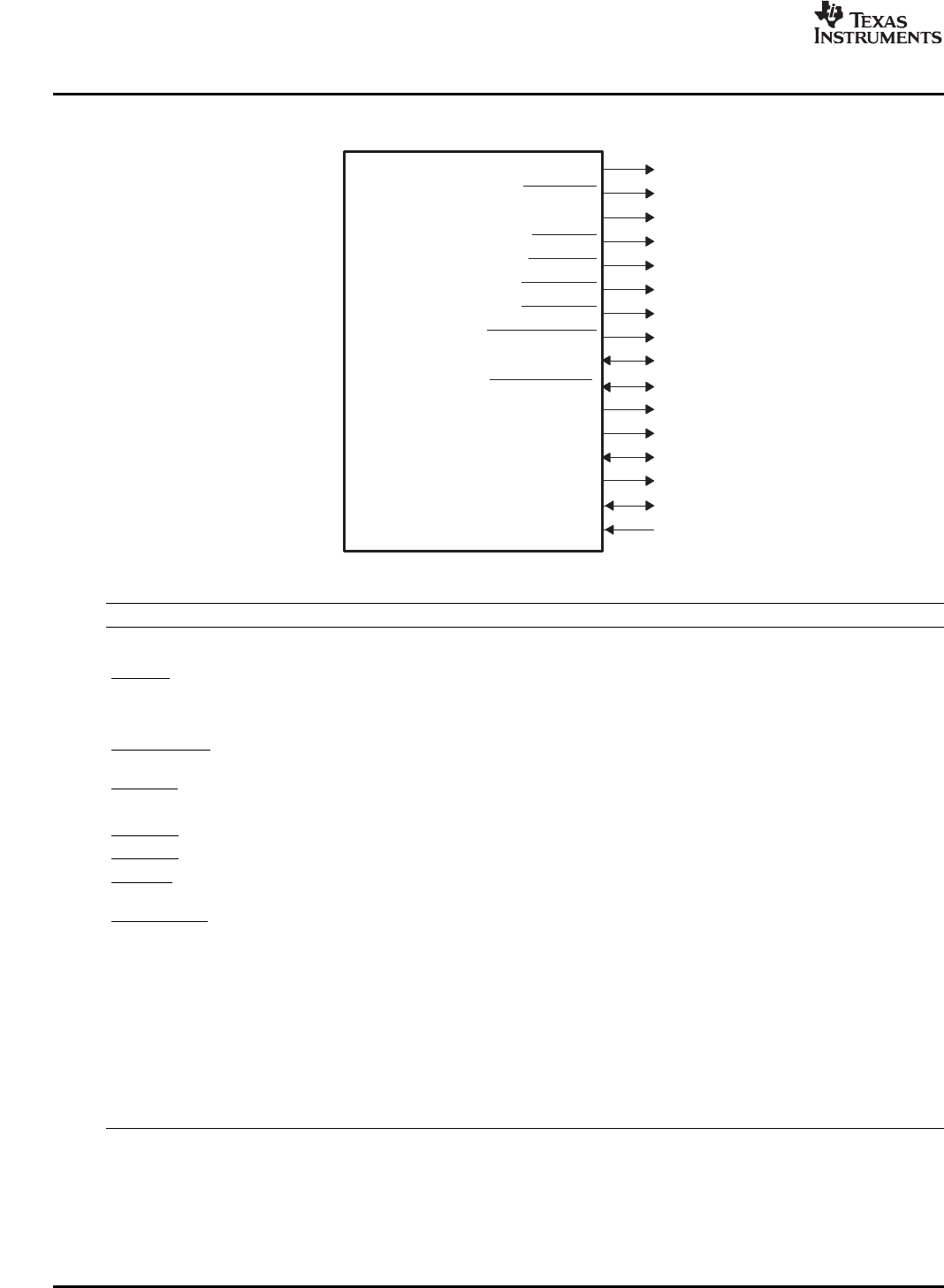

DDR_D[31:0]

DDR2

memory

controller

DDR_CLK

DDR_CLK

DDR_CS

DDR_CKE

DDR_RAS

DDR_WE

DDR_DQM[3:0]

DDR_CAS

DDR_BA[2:0]

DDR_DQS[3:0]

DDR_A[13:0]

DDR_VREF

DDR_DQGATE[3:0]

DDR_DQS[3:0]

DDR_ODT[1:0]

PeripheralArchitecture

Figure2.DDR2MemoryControllerSignals

Table1.DDR2MemoryControllerSignalDescriptions

PinDescription

DDR_D[31:0]Bidirectionaldatabus.Inputfordatareadsandoutputfordatawrites.

DDR_A[13:0]Externaladdressoutput.

DDR_CSActive-lowchipenableformemoryspaceCE0.DDR_CSisusedtoenabletheDDR2SDRAMmemory

deviceduringexternalmemoryaccesses.DDR_CSpinstayslowthroughouttheoperationoftheDDR2

memorycontroller;itnevergoeshigh.NotethatthisbehaviordoesnotaffecttheabilityoftheDDR2memory

controllertoaccessDDR2SDRAMmemorydevices.

DDR_DQM[3:0]Active-lowoutputdatamask.

DDR_CLK/Differentialclockoutputs.

DDR_CLK

DDR_CKEClockenable(usedforself-refreshmode).

DDR_CASActive-lowcolumnaddressstrobe.

DDR_RASActive-lowrowaddressstrobe.

DDR_WEActive-lowwriteenable.

DDR_DQS[3:0]/Differentialdatastrobebidirectionalsignals.

DDR_DQS[3:0]

DDR_ODT[1:0]On-dieterminationsignalstoexternalDDR2SDRAM.Thesepinsarereservedforfutureuseandshouldnot

beconnectedtotheDDR2SDRAM.Note:therearenoon-dieterminationresistorsimplementedonthedie

ofthisdevice.

DDR_BA[2:0]Bank-addresscontroloutputs.

DDR_DQGATE[3:0]Datastrobegatepins.Thesepinsareusedasatimingreferenceduringmemoryreads.The

DDR_DQGATE0andDDR_DQGATE2pinsshouldberoutedoutandconnectedtotheDDR_DQGATE1and

DDR_DQGATE3pins,respectively.Formoreroutingrequirementsonthesepins,seethedevice-specific

datamanual.

DDR_VREFDDR2MemoryControllerreferencevoltage.Thisvoltagemustbesuppliedexternally.Seethe

device-specificdatamanualformoredetails.

DSPDDR2MemoryController 12SPRUEK5A–October2007

SubmitDocumentationFeedback