www.ti.com

2.4.1ModeRegisterSet(MRSandEMRS)

COL

MRS/EMRS

BANK

DDR_CLK

DDR_CLK

DDR_CS

DDR_CKE

DDR_RAS

DDR_WE

DDR_CAS

DDR_BA[2:0]

DDR_A[13:0]

2.4.2RefreshMode

PeripheralArchitecture

DDR2SDRAMcontainsmodeandextendedmoderegistersthatconfiguretheDDR2memoryfor

operation.Theseregisterscontrolbursttype,burstlength,CASlatency,DLLenable/disable,single-ended

strobe,etc.

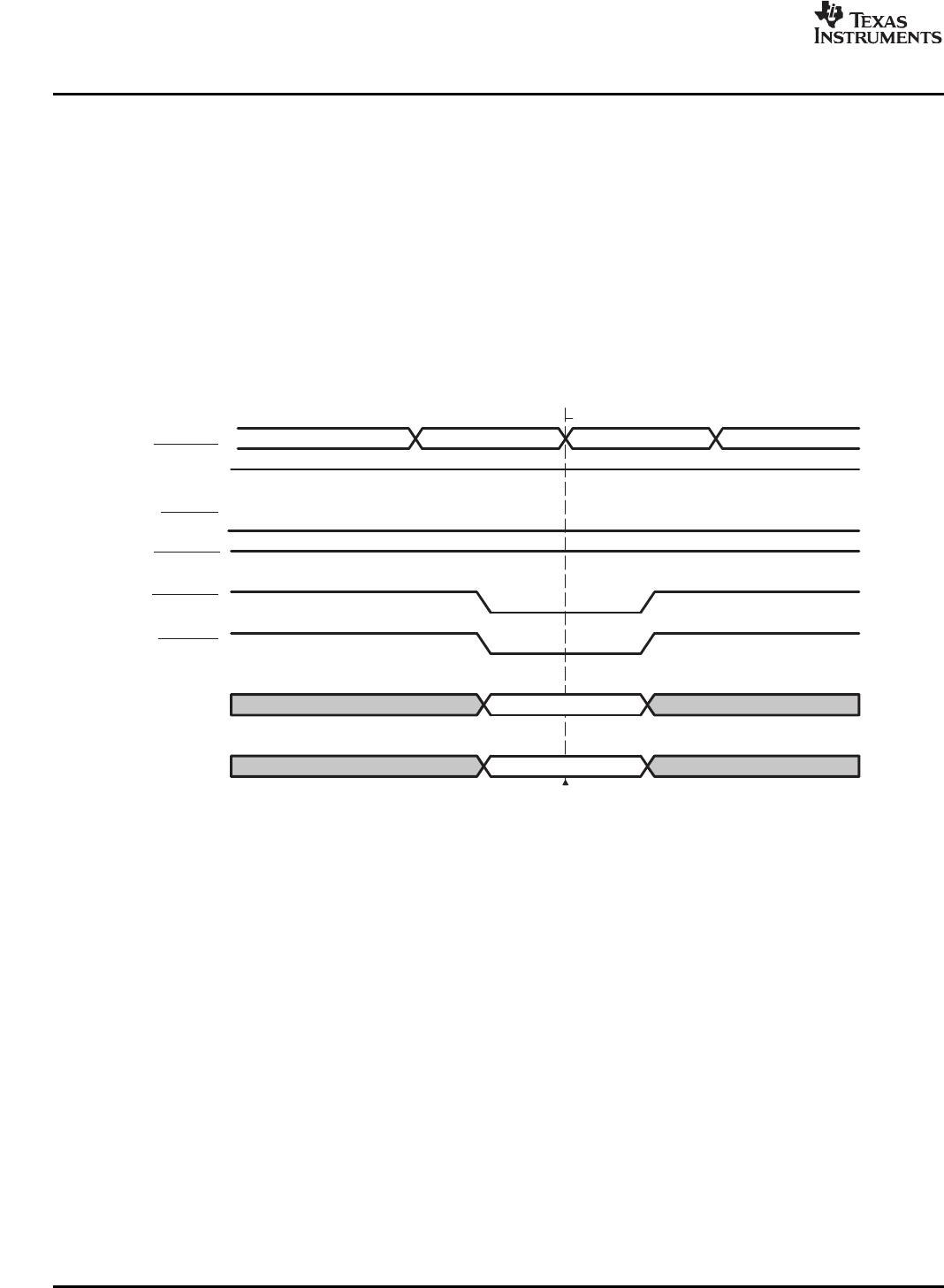

TheDDR2memorycontrollerprogramsthemodeandextendedmoderegistersoftheDDR2memoryby

issuingMRSandEMRScommands.WhentheMRSorEMRScommandisexecuted,thevalueon

DDR_BA[1:0]selectsthemoderegistertobewrittenandthedataonDDR_A[12:0]isloadedintothe

register.Figure3showsthetimingforanMRSandEMRScommand.

TheDDR2memorycontrolleronlyissuesMRSandEMRScommandsduringtheDDR2memorycontroller

initializationsequence.SeeSection2.11formoreinformation.

Figure3.DDR2MRSandEMRSCommand

TheDDR2memorycontrollerissuesrefreshcommandstotheDDR2SDRAMdevice(Figure4).REFRis

automaticallyprecededbyaDCABcommand,ensuringthedeactivationofallCEspacesandbanks

selected.FollowingtheDCABcommand,theDDR2memorycontrollerbeginsperformingrefreshesata

ratedefinedbytherefreshrate(REFRESH_RATE)bitintheSDRAMrefreshcontrolregister(SDRFC).

PageinformationisalwaysinvalidbeforeandafteraREFRcommand;thus,arefreshcyclealwaysforces

apagemiss.Thistypeofrefreshcycleisoftencalledautorefresh.Autorefreshcommandsmaynotbe

disabledwithintheDDR2memorycontroller.SeeSection2.8formoredetailsonREFRcommand

scheduling.

14DSPDDR2MemoryControllerSPRUEK5A–October2007

SubmitDocumentationFeedback