www.ti.com

4.4SDRAMRefreshControlRegister(SDRFC)

DDR2MemoryControllerRegisters

TheSDRAMrefreshcontrolregister(SDRFC)isusedtoconfiguretheDDR2memorycontrollerto:

•EnterandExittheself-refreshstate.

•MeettherefreshrequirementoftheattachedDDR2devicebyprogrammingtherateatwhichthe

DDR2memorycontrollerissuesautorefreshcommands.

TheSDRFCisshowninFigure23anddescribedinTable21.

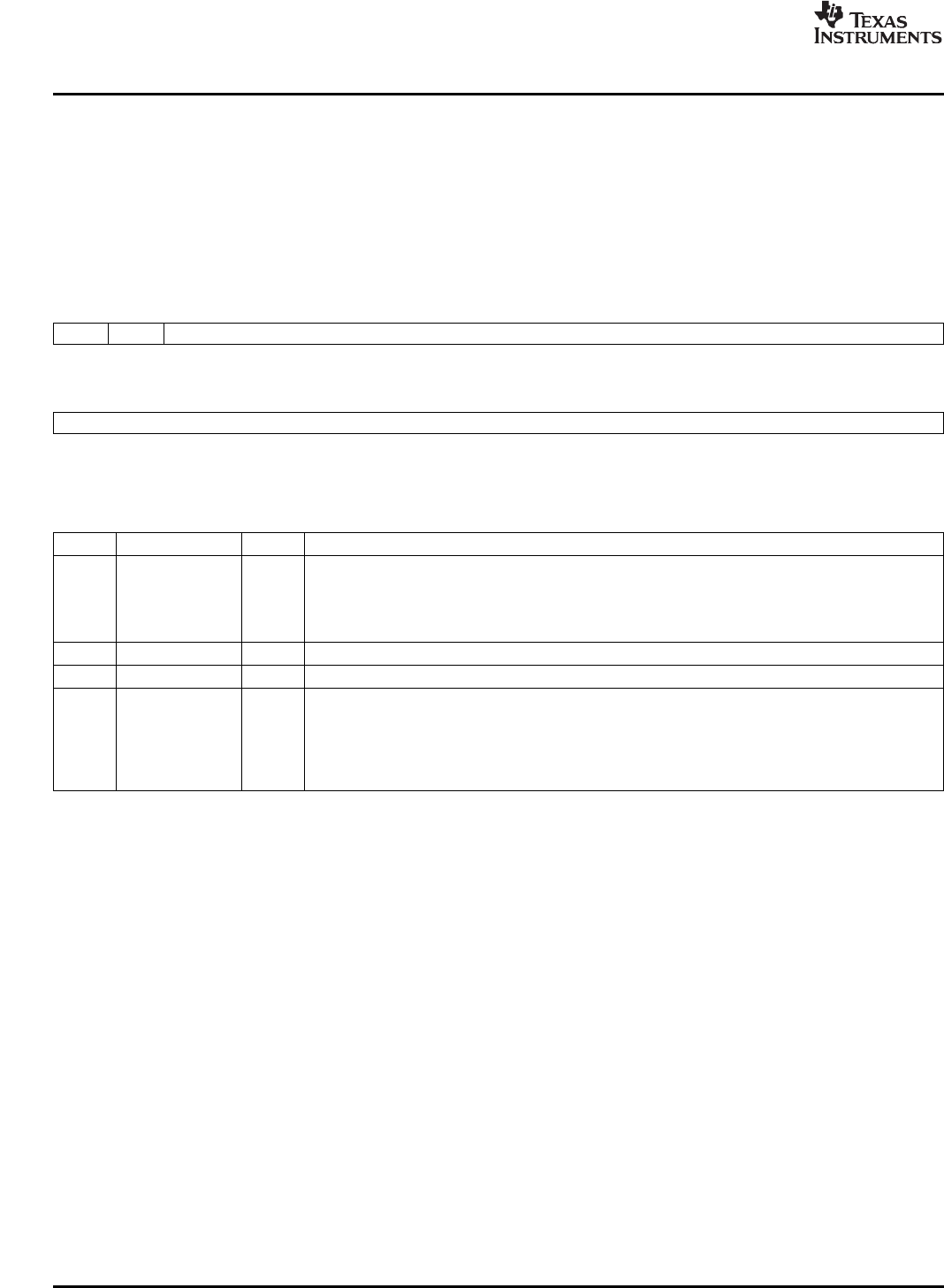

Figure23.SDRAMRefreshControlRegister(SDRFC)

31302916

SRRsvdReserved

R/W-R/W-R-0x0

0x00x0

150

REFRESH_RATE

R/W-0x753

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table21.SDRAMRefreshControlRegister(SDRFC)FieldDescriptions

BitFieldValueDescription

31SRSelf-refreshbit.Writinga1tothisbitwillcauseconnectedSDRAMdevicestobeplaceintoSelf

RefreshmodeandtheDDR2MemoryControllertoentertheSelfRefreshstate.

0Exitself-refreshmode.

1Enterself-refreshmode.

30ReservedReserved.Writestothisregistermustkeepthisfieldatitsdefaultvalue.

29-16ReservedReserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

15-0REFRESH_RATERefreshratebits.ThevalueinthisfieldisusedtodefinetherateatwhichconnectedSDRAM

deviceswillberefreshedasfollows:effect.

SDRAMrefreshrate=DDR_CLKclockrate/REFRESH_RATE

Writingavaluelessthan0x0100tothisfieldwillcauseittobeloadedwith2*T_RFCvaluefrom

theSDRAMTiming1Register.

40DSPDDR2MemoryControllerSPRUEK5A–October2007

SubmitDocumentationFeedback