www.ti.com

4.8DDR2MemoryControllerControlRegister(DMCCTL)

DDR2MemoryControllerRegisters

TheDDR2memorycontrollercontrolregister(DMCCTL)resetstheinterfacelogicoftheDDR2memory

controller.TheDMCCTLisshowninFigure27anddescribedinTable25.

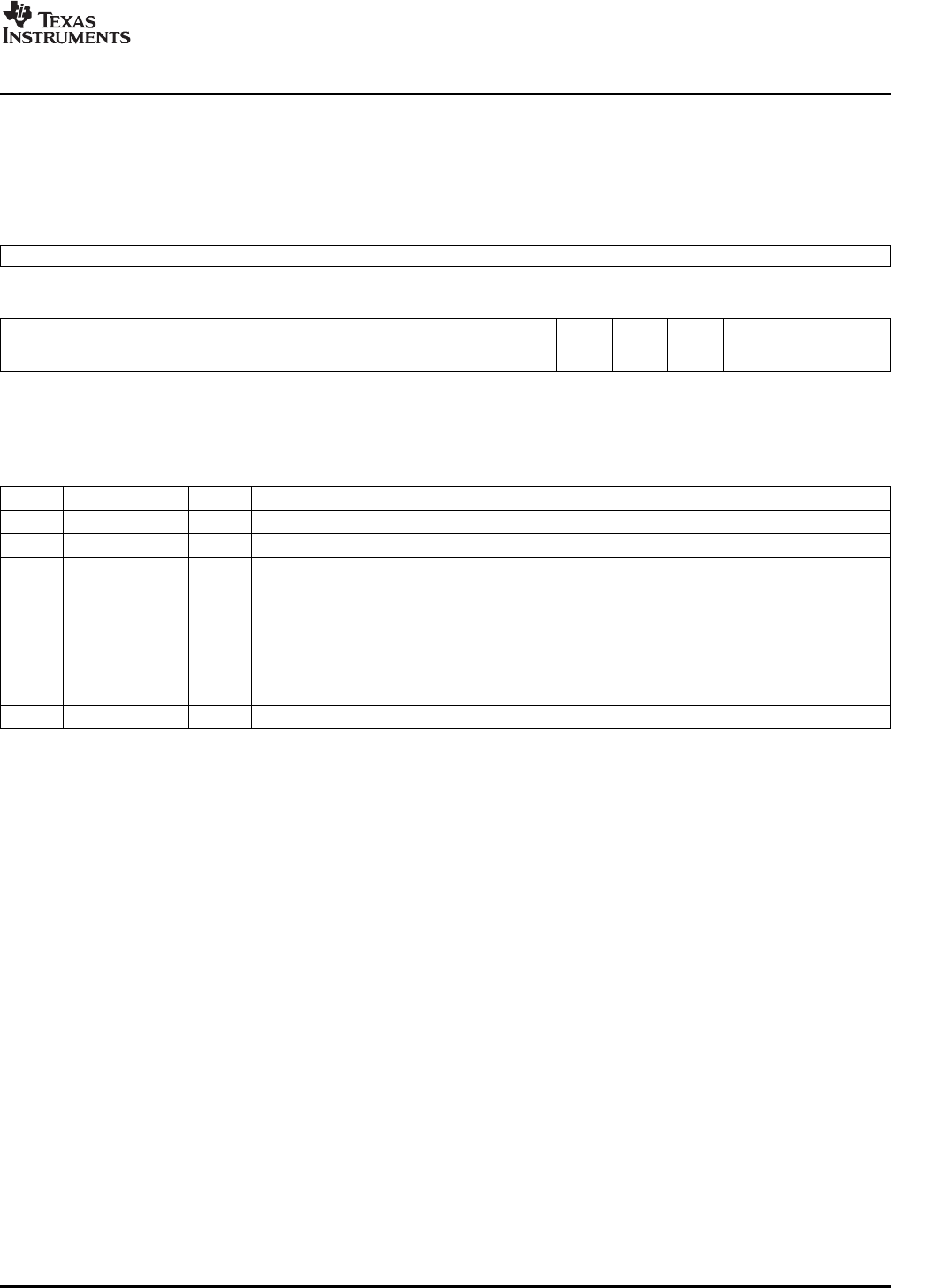

Figure27.DDR2MemoryControllerControlRegister(DMCCTL)

3116

Reserved

R-0x5000

15654320

IF

ReservedRESERsvdRsvdRL

T

R/W-0x0190R/W-R/W-R-0x0R/W-0x7

0x10x0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table25.DDR2MemoryControllerControlRegister(DMCCTL)FieldDescriptions

BitFieldValueDescription

31-6ReservedReserved.Writestothisregistermustkeepthisfieldatitsdefaultvalue.

15-6ReservedReserved.Writestothisregistermustkeepthisfieldatitsdefaultvalue.

5IFRESETDDR2memorycontrollerinterfacelogicreset.Theinterfacelogiccontrolsthesignalsusedto

communicatewithDDR2SDRAMdevices.Thisbitresetstheinterfacelogic.Thestatusofthis

interfacelogicisshownontheDDR2memorycontrollerstatusregister.

0Releasereset.

1Assertreset.

4ReservedReserved.Writestothisregistermustkeepthisfieldatitsdefaultvalue.

3ReservedReserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

2-0RLReadlatencybits.ThesebitsmustbesetequaltotheCASlatencyplus1.

SPRUEK5A–October2007DSPDDR2MemoryController45

SubmitDocumentationFeedback