www.ti.com

DDR2MemoryControllerRegisters

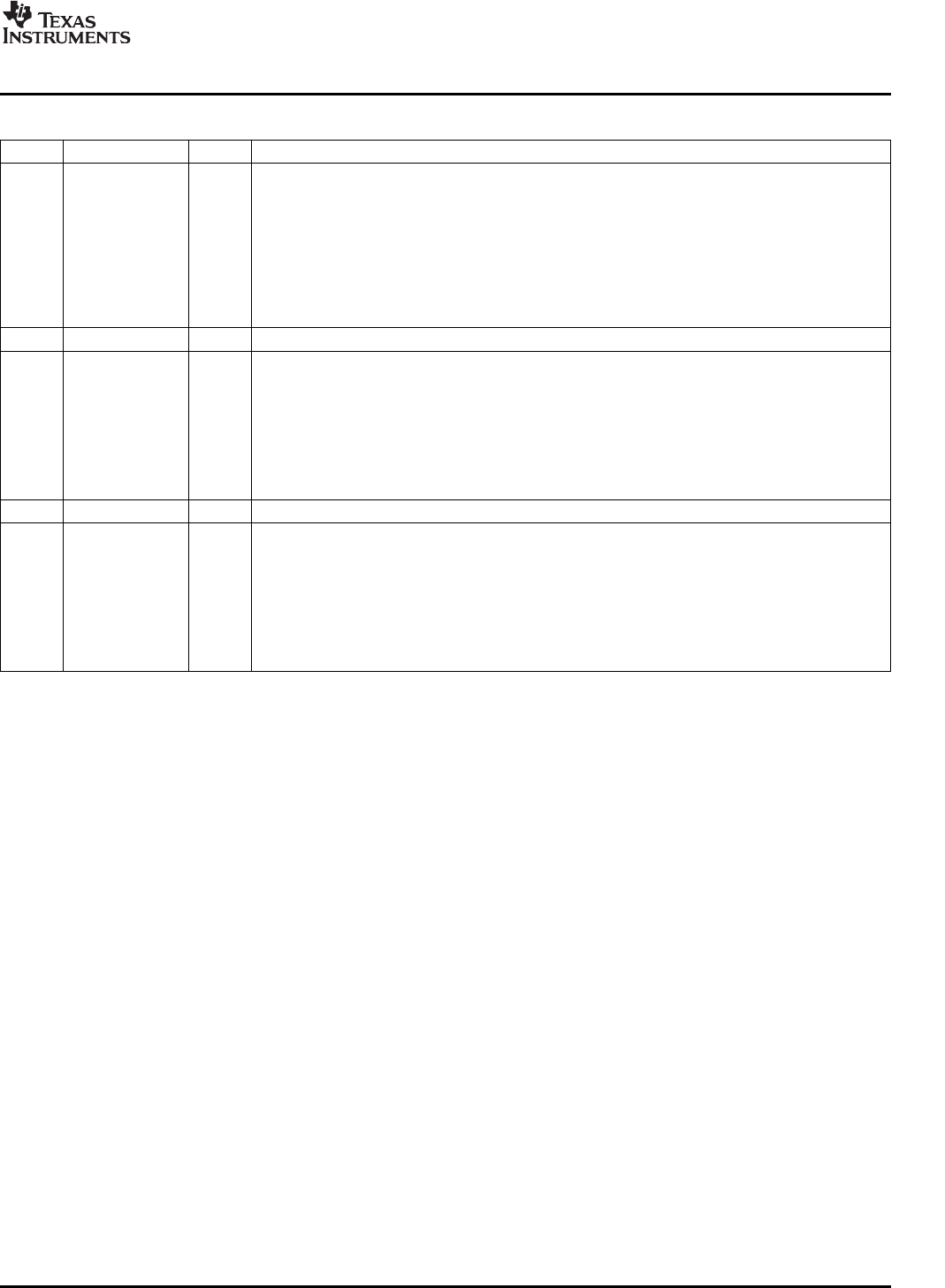

Table20.SDRAMConfigurationRegister(SDCFG)FieldDescriptions(continued)

BitFieldValueDescription

11-9CLCASlatency.ThevalueofthisfielddefinestheCASlatency,tobeusedwhenaccessingconnected

SDRAMdevices.AwritetothisfieldwillcausetheDDR2MemoryControllertostarttheSDRAM

initializationsequence.ThisfieldiswriteableonlywhentheTIMUNLOCKbitisunlocked.Values0,

1,6,and7arereservedforthisfield.

2CASlatencyof2

3CASlatencyof3

4CASlatencyof4

5CASlatencyof5

8-7ReservedReserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

6-4IBANKInternalSDRAMbanksetupbits.DefinesnumberofbanksinsideconnectedSDRAMdevices.A

writetothisbitwillcausetheDDR2MemoryControllertostarttheSDRAMinitializationsequence.

Values4-7arereservedforthisfield.

0OnebankSDRAMdevices

1TwobanksSDRAMdevices

2FourbanksSDRAMdevices

3EightbanksSDRAMdevices

3ReservedReserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

2-0PAGESIZEPagesizebits.DefinestheinternalpagesizeoftheexternalDDR2memory.Awritetothisbitwill

causetheDDR2MemoryControllertostarttheSDRAMinitializationsequence.Values0,1,6,and

7arereservedforthisfield.Values4-7arereservedforthisfield.

0256-wordpagerequiring8columnaddressbits.

1512-wordpagerequiring9columnaddressbits.

21024-wordpagerequiring10columnaddressbits.

32048-wordpagerequiring11columnaddressbits.

SPRUEK5A–October2007DSPDDR2MemoryController39

SubmitDocumentationFeedback