www.ti.com

4.5SDRAMTiming1Register(SDTIM1)

DDR2MemoryControllerRegisters

TheSDRAMtiming1register(SDTIM1)configurestheDDR2memorycontrollertomeetmanyoftheAC

timingspecificationoftheDDR2memory.NotethatDDR_CLKisequaltotheperiodoftheDDR_CLK

signal.SeetheDDR2memorydatasheetforinformationontheappropriatevaluestoprogrameachfield.

ThebitfieldsintheSDTIM1registerareonlywriteablewhentheTIMUNLOCKbitoftheSDRAM

Configurationregister(SDCFG)isunlocked.TheSDTIM1isshowninFigure24anddescribedin

Table22.

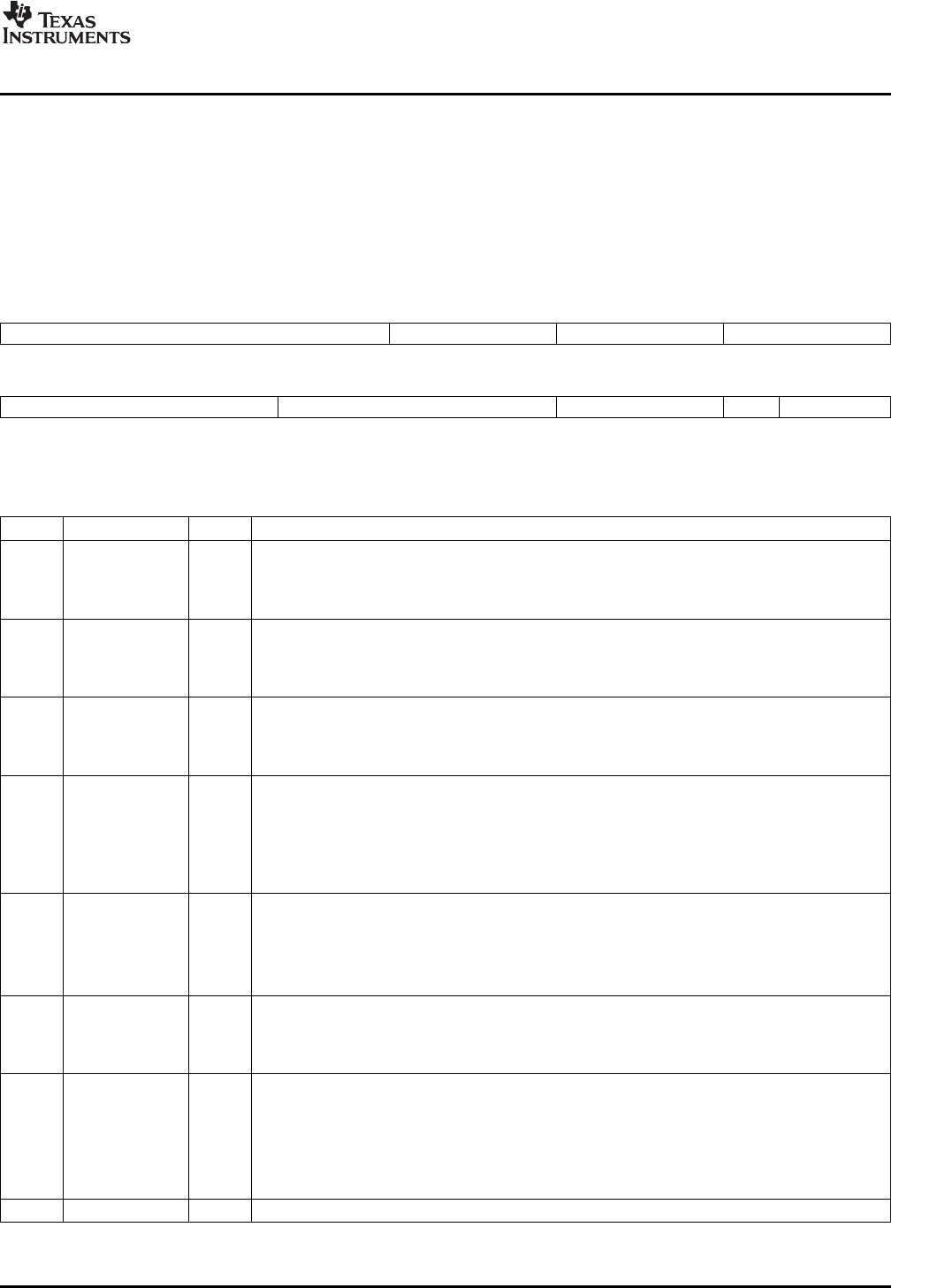

Figure24.SDRAMTiming1Register(SDTIM1)

3125242221191816

T_RFCT_RPT_RCDT_WR

R/W-0x3FR/W-0x7R/W-0x7R/W-0x7

151110653210

T_RAST_RCT_RRDRsvdT_WTR

R/W-0x1FR/W-0x1FR/W-0x7R-0R/W-0x3

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table22.SDRAMTiming1Register(SDTIM1)FieldDescriptions

BitFieldValueDescription

31-25T_RFCThesebitsspecifytheminimumnumberofDDR_CLKcyclesfromarefreshorloadmodecommand

toarefreshoractivatecommand,minusone.Thevalueforthesebitscanbederivedfromthet

rfc

ACtimingparameterintheDDR2memorydatasheet.Calculateusingthisformula:

T_RFC=(t

rfc

/DDR_CLK)-1

24-22T_RPThesebitsspecifytheminimumnumberofDDR_CLKcyclesfromaprechargecommandtoa

refreshoractivatecommand,minus1.Thevalueforthesebitscanbederivedfromthet

rp

AC

timingparameterintheDDR2memorydatasheet.Calculateusingtheformula:

T_RP=(t

rp

/DDR_CLK)-1

21-19T_RCDThesebitsspecifytheminimumnumberofDDR_CLKcyclesfromanactivatecommandtoaread

orwritecommand,minus1.Thevalueforthesebitscanbederivedfromthet

rcd

ACtiming

parameterintheDDR2memorydatasheet.Calculateusingtheformula:

T_RCD=(t

rcd

/DDR_CLK)-1

18-16T_WRThesebitsspecifytheminimumnumberofDDR_CLKcyclesfromthelastwritetransfertoa

prechargecommand,minus1.Thevalueforthesebitscanbederivedfromthet

wr

ACtiming

parameterintheDDR2memorydatasheet.Calculateusingtheformula:

T_WR=(t

wr

/DDR_CLK)-1

TheSDRAMinitializationsequencewillbestartedwhenthevalueofthisfieldischangedfromthe

previousvalueandtheDDR2_ENABLEinSDCFGisequalto1.

15-11T_RASThesebitsspecifytheminimumnumberofDDR_CLKcyclesfromanactivatecommandtoa

prechargecommand,minus1.Thevalueforthesebitscanbederivedfromthet

ras

ACtiming

parameterintheDDR2memorydatasheet.Calculateusingthisformula:

T_RAS=(t

ras

/DDR_CLK)-1

T_RASmustbegreaterthanorequaltoT_RCD.

10-6T_RCThesebitsspecifytheminimumnumberofDDR_CLKcyclesfromanactivatecommandtoan

activatecommand,minus1.Thevalueforthesebitscanbederivedfromthet

rc

ACtiming

parameterintheDDR2memorydatasheet.Calculateusingthisformula:

T_RC=(t

rc

/DDR_CLK)-1

5-3T_RRDThesebitsspecifytheminimumnumberofDDR_CLKcyclesfromanactivatecommandtoan

activatecommandinadifferentbank,minus1.Thevalueforthesebitscanbederivedfromthet

rrd

ACtimingparameterintheDDR2memorydatasheet.Calculateusingthisformula:

T_RRD=(t

rrd

/DDR_CLK)-1

Whenconnectingtoan8_bankDDR2SDRAM,thisfieldmustbeequalto:

T_RRD=((4*t

rrd

+2*t

ck

)/(4*t

ck

))-1

2ReservedReserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

SPRUEK5A–October2007DSPDDR2MemoryController41

SubmitDocumentationFeedback