www.ti.com

2.4ProtocolDescription(s)

PeripheralArchitecture

TheDDR2memorycontrollersupportstheDDR2SDRAMcommandslistedinTable2.Table3showsthe

signaltruthtablefortheDDR2SDRAMcommands.

Table2.DDR2SDRAMCommands

CommandFunction

ACTVActivatestheselectedbankandrow.

DCABPrechargeallcommand.Deactivates(precharges)allbanks.

DEACPrechargesinglecommand.Deactivates(precharges)asinglebank.

DESELDeviceDeselect.

EMRSExtendedModeRegisterset.Allowsalteringthecontentsofthemoderegister.

MRSModeregisterset.Allowsalteringthecontentsofthemoderegister.

NOPNooperation.

PowerDownPowerdownmode.

READInputsthestartingcolumnaddressandbeginsthereadoperation.

READwithInputsthestartingcolumnaddressandbeginsthereadoperation.Thereadoperationisfollowedbya

autoprechargeprecharge.

REFRAutorefreshcycle.

SLFREFRSelf-refreshmode.

WRTInputsthestartingcolumnaddressandbeginsthewriteoperation.

WRTwithInputsthestartingcolumnaddressandbeginsthewriteoperation.Thewriteoperationisfollowedbya

autoprechargeprecharge.

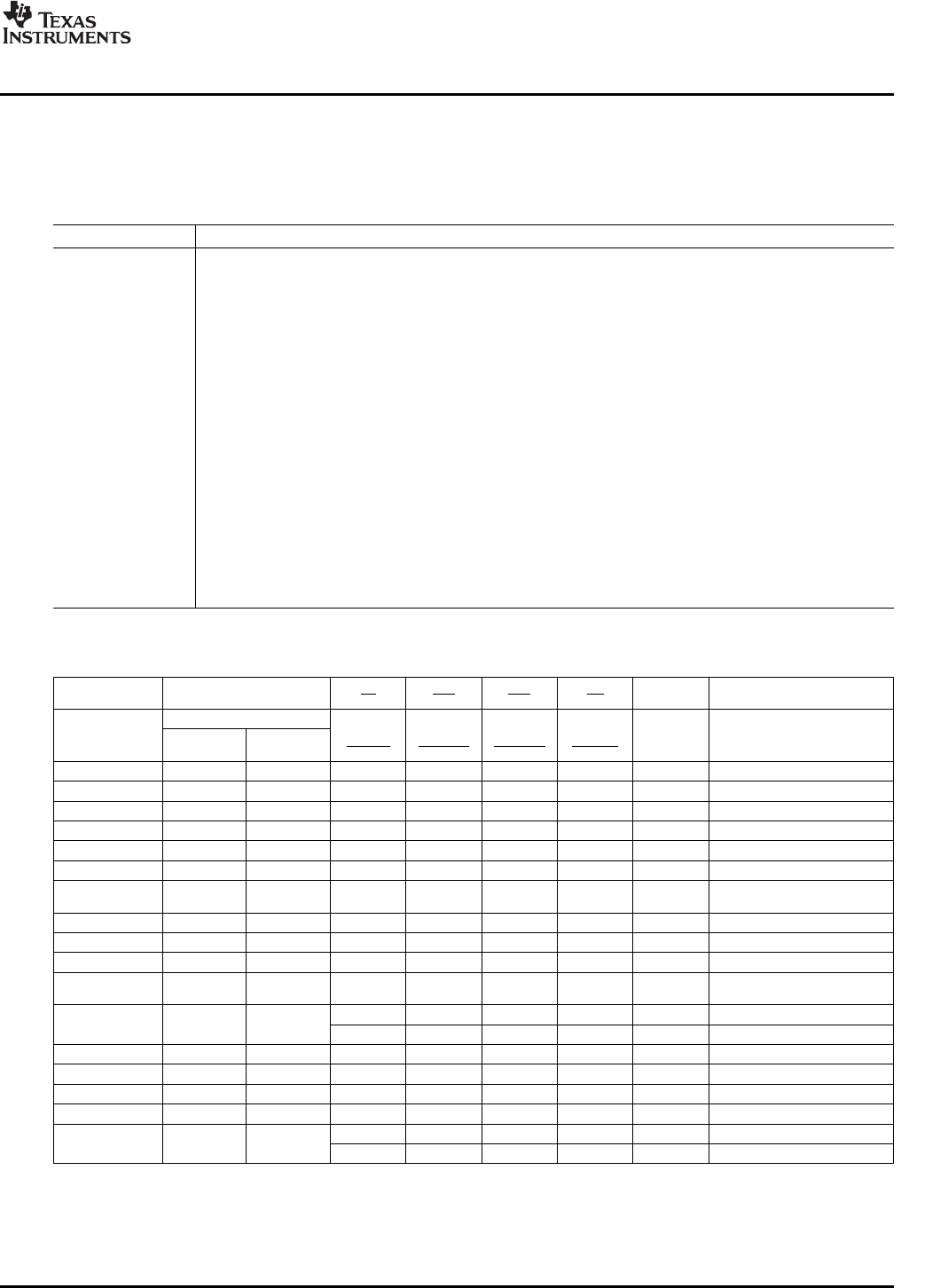

Table3.TruthTableforDDR2SDRAMCommands

DDR2SDRAM

SignalsCKECSRASCASWEBA[2:0]A[13:11,9:0]A10

DDR_CKE

DDR2MemoryPreviousDDR_BA[2:0

ControllerSignalsCyclesCurrentCycleDDR_CSDDR_RASDDR_CASDDR_WE]DDR_A[13:11,9:0]DDR_A[10]

ACTVH

(1)

HLLHHBankRowAddress

DCABHHLLHLXXL

DEACHHLLHLBankXL

MRSHHLLLLBA

(2)

OPCode

EMRSHHLLLLBAOPCode

READHHLHLHBAColumnAddressL

READwithHHLHLHBAColumnAddressH

precharge

WRTHHLHLLBAColumnAddressL

WRTwithprechargeHHLHLLBAColumnAddressL

REFRHHLLLHXXX

SLFREFRHLLLLHXXX

entry

SLFREFRLHHXXXXXX

exit

LHHHXXX

NOPHXLHHHXXX

DESELHXHXXXXXX

PowerDownentryHLHXXXXXX

LHHHXXX

PowerDownexitLHHXXXXXX

LHHHXXX

(1)

Legend:Hmeanslogichigh;Lmeanslogiclow;Xmeansdon'tcare(eitherHorL).

(2)

BAreferstothebankaddresspins(BA[2:0]).

SPRUEK5A–October2007DSPDDR2MemoryController13

SubmitDocumentationFeedback