Chapter 5 Input/Output Interfaces

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition – September 1997

5-24

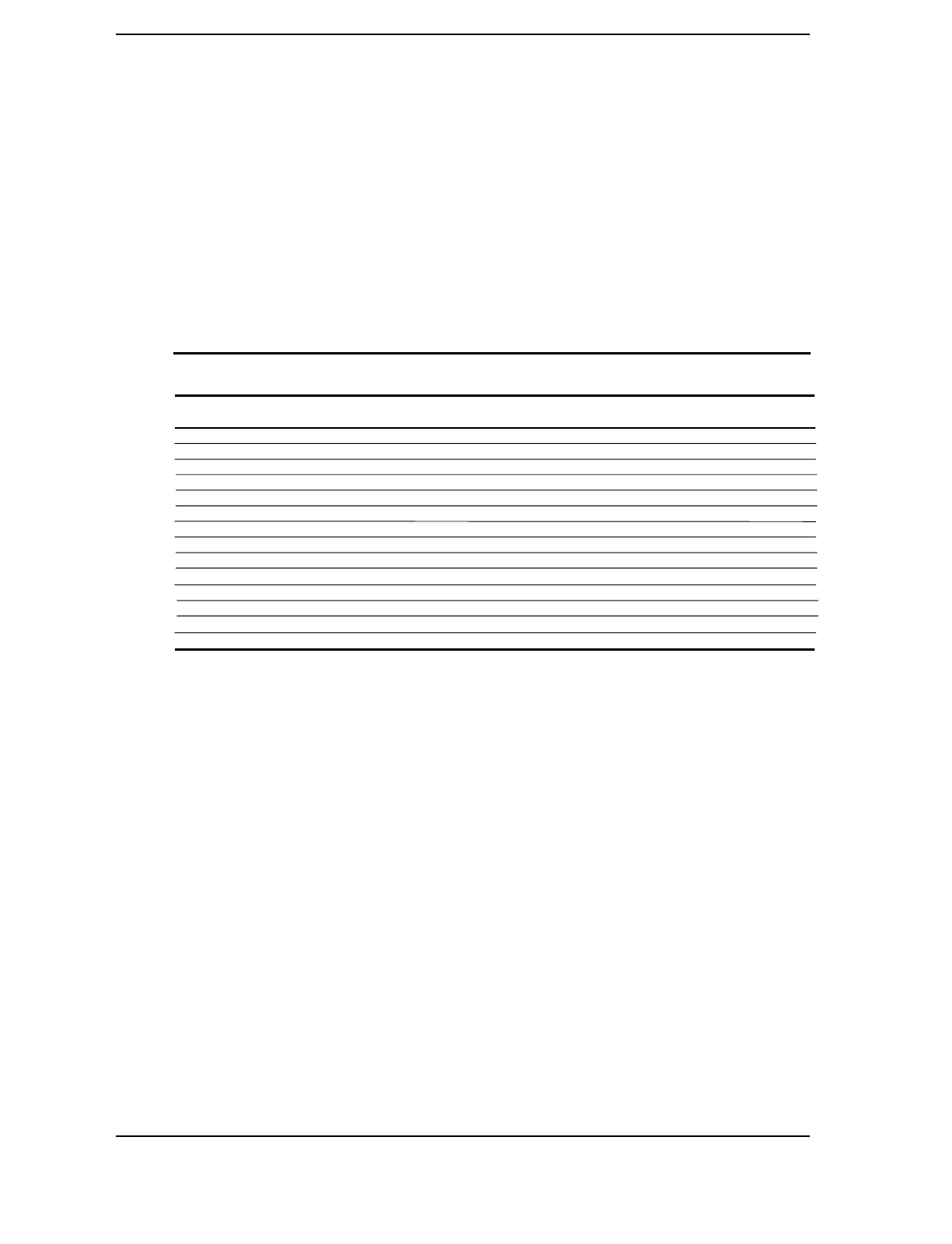

5.5.4.2 Parallel Interface Control

The BIOS function INT 17 provides simplified control of the parallel interface. Basic functions

such as initialization, character printing, and printer status are provide by subfunctions of INT

17. The parallel interface is controllable by software through a set of I/O mapped registers. The

number and type of registers available depends on the mode used (SPP, EPP, or ECP). Table 5-14

lists the parallel registers and associated functions based on mode.

Table 5–14.

Parallel Interface Control Registers

Table 5-14.

Parallel Interface Control Registers

Register

I/O

Address

SPP Mode

Ports

EPP Mode

Ports

ECP Mode

Ports

Data Base LPT1,2,3 LPT1,2 LPT1,2,3

Status Base + 1h LPT1,2,3 LPT1,2 LPT1,2,3

Control Base + 2h LPT1,2,3 LPT1,2 LPT1,2,3

Address Base + 3h -- LPT1,2 --

Data Port 0 Base + 4h -- LPT1,2 --

Data Port 1 Base + 5h -- LPT1,2 --

Data Port 2 Base + 6h -- LPT1,2 --

Data Port 3 Base + 7h -- LPT1,2 --

Parallel Data FIFO Base + 400h -- -- LPT1,2,3

ECP Data FIFO Base + 400h -- -- LPT1,2,3

Test FIFO Base + 400h -- -- LPT1,2,3

Configuration Register A Base + 400h -- -- LPT1,2,3

Configuration Register B Base + 401h -- -- LPT1,2,3

Extended Control Register Base + 402h -- -- LPT1,2,3

Base Address:

LPT1 = 378h

LPT2 = 278h

LPT3 = 3BCh

The following paragraphs describe the individual registers. Note that only the LPT1-based

addresses are given in these descriptions.

Data Register, I/O Port 378h

Data written to this register is presented to the data lines D0-D7. A read of this register when in

SPP-compatible mode yields the last byte written. A read while in SPP-extended or ECP mode

yields the status of data lines D0-D7 (i.e., receive data).

In ECP mode in the forward (output) direction, a write to this location places a tagged command

byte into the FIFO and reads have no effect.