Chapter 4 System Support

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition - September 1997

4-4

4.2.2 PCI BUS MASTER ARBITRATION

The PCI bus supports a bus master/target arbitration scheme. A bus master is a device that has

been granted control of the bus for the purpose of initiating a transaction. A target is a device that

is the recipient of a transaction. Request (REQ), Grant (GNT), and FRAME signals are used by

PCI bus masters for gaining access to the PCI bus. When a PCI device needs access to the PCI

bus (and does not already own it), the PCI device asserts it’s REQn signal to the PCI bus arbiter

(a function of the system controller component). If the bus is available, the arbiter asserts the

GNTn signal to the requesting device, which then asserts FRAME and conducts the address

phase of the transaction with a target. If the PCI device already owns the bus, a request is not

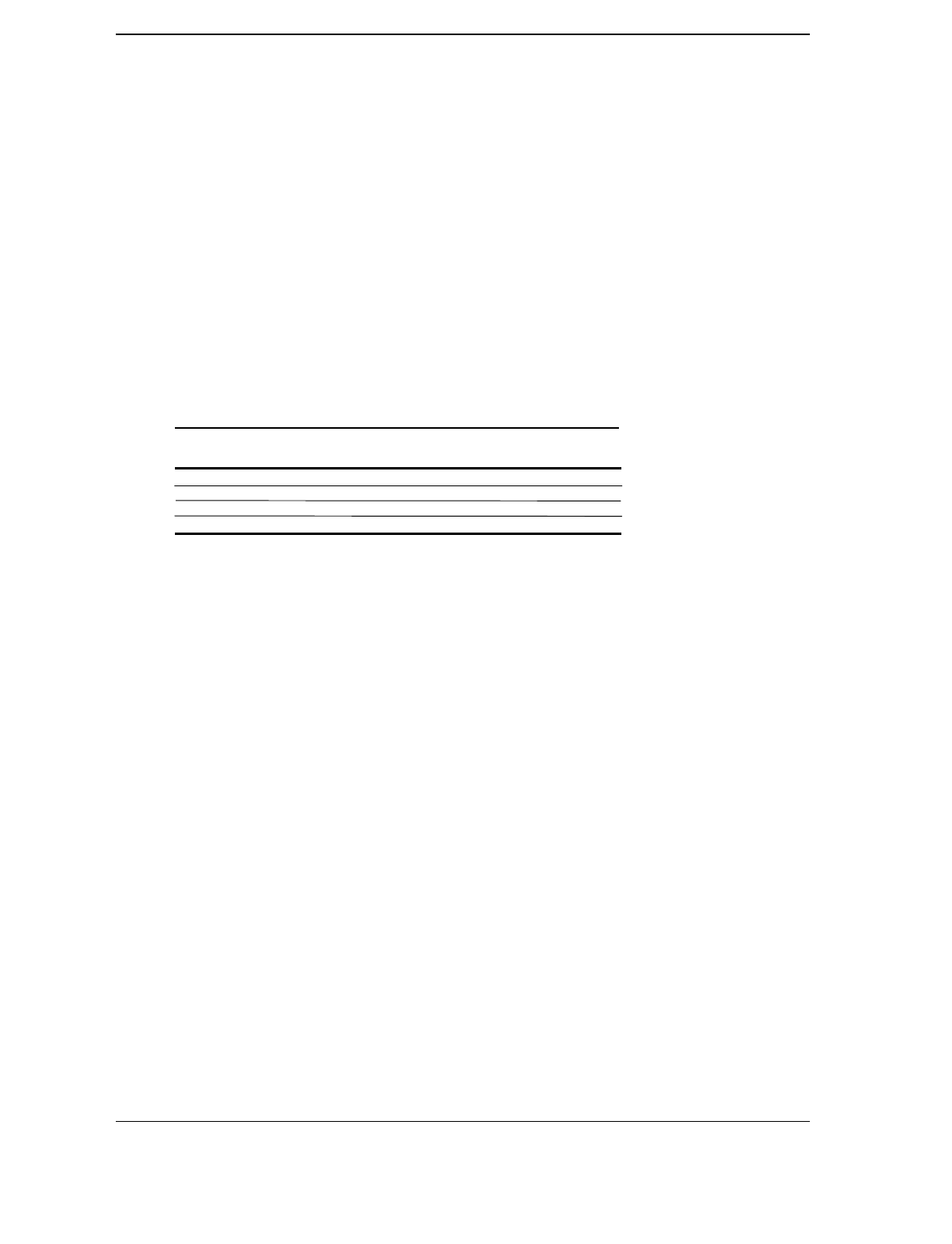

needed and the device can simply assert FRAME and conduct the transaction. Table 4-1 shows

the grant and request signals assignments for the devices on the PCI bus.

Table 4–2.

PCI Bus Mastering Devices

Table 4-2.

PCI Bus Mastering Devices

REQ/GNT Line Device

REQ1/GNT1 PCI Connector

REQ2/GNT2 Graphics Controller

REQ3/GNT3 Network I/F Controller

PCI bus control is granted according to a Least Recently Used (LRU) algorithm. During times

that the bus is not used or requested, bus control is given to the Host/PCI bridge. After a device

has given up control of the bus or has not executed a transaction for 16 PCI clock cycles

(PCICLKs) after gaining bus control, it loses access and is placed on the bottom of the priority

list.

The PCI/ISA bridge is given special consideration. If the PCI/ISA bridge gains control of the PCI

bus but does not execute a transaction after 16 PCICLKs, the PCI/ISA bridge retains ownership

of the PCI bus until the current ISA bus master relinquishes the ISA bus. The PCI/ISA bridge is

then placed on the bottom of the priority list.

PCI bus priority can be altered in two ways: by a master needing to perform a retry of a data

cycle, or by the master locking the bus. When a master is retried, it releases the bus and negates

its REQn- line for a minimum of two PCICLKs and then requests the bus again. If the master is

granted the bus before the condition that caused the retry is resolved, the master is retried again,

which may result in bus “thrashing.” Bus thrashing is minimized by masking the REQn- line of a

particular device that has had a transaction retried.

If a master locks the PCI bus, it retains top priority, allowing it to quickly finish a lock sequence.

The PCI/ISA bridge cannot become master until the locking device unlocks the bus.

Consequently, a master should not lock the bus for long periods of time or latency problems could

occur.