Chapter 4 System Support

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition - September 1997

4-22

4.3.5 INTERVAL TIMER

The interval timer generates pulses at software (programmable) intervals. A 8254-compatible

timer is integrated into the South Bridge chip. The timer function provides three counters, the

functions of which are listed in Table 4-13.

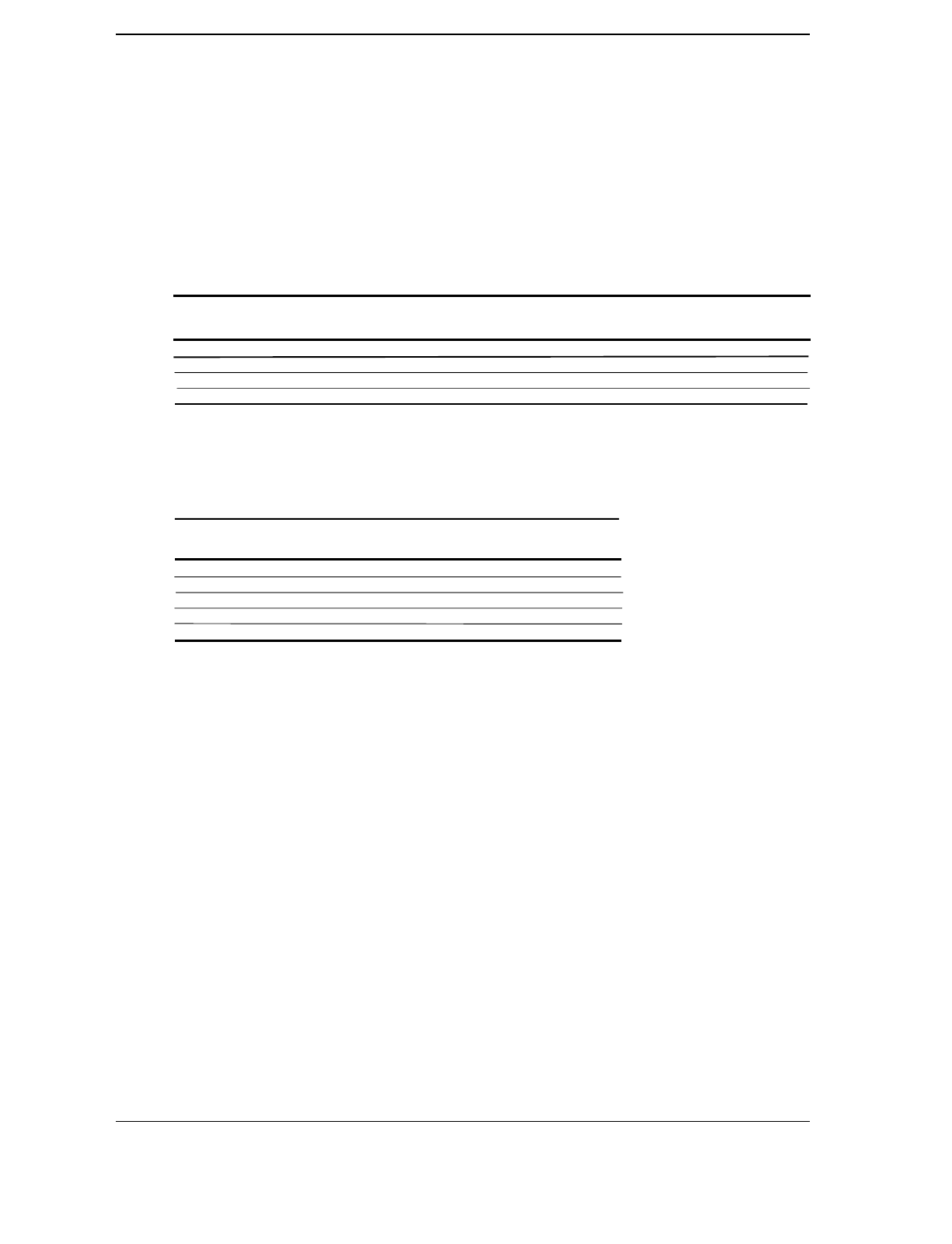

Table 4–13.

Interval Timer Functions

Table 4-13.

Interval Timer Functions

Counter Function Gate Clock In Clock Out

0 System Clock Always on 1.193 MHz IRQ0

1 Refresh Always on 1.193 MHz Refresh Req.

2 Speaker Tone Port 61, bit<0> 1.193 MHz Speaker Input

The interval timer is controlled through the I/O mapped registers listed in Table 4-14.

Table 4–14.

Interval Timer Control Registers

Table 4-14.

Interval Timer Control Registers

I/O Port Register

040h Read or write value, counter 0

041h Read or write value, counter 1

042h Read or write value, counter 2

043h Control Word

Interval timer operation follows standard AT-type protocol. For a detailed description of timer

registers and operation, refer to the Compaq Extended Industry Standard Architecture Expansion

Bus Technical Reference Guide.

4.3.6 ISA CONFIGURATION

The working relationship between the PCI and ISA buses requires that certain parameters be

configured. The PC/ISA bridge function of the South Bridge component includes configuration

registers to set parameters such as PCI IRQ routing and top-of-memory available to ISA/DMA

devices. These parameters are programmed by BIOS during power-up, using registers listed

previously in Table 4-6.