Chapter 4 System Support

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition - September 1997

4-18

4.3.4 INTERRUPTS

The microprocessor uses two types of interrupts; maskable and nonmaskable. A maskable

interrupt can be enabled or disabled within the microprocessor by the use of the STI and CLI

instructions. A nonmaskable interrupt cannot be masked off within the microprocessor but may

be inhibited by hardware or software means external to the microprocessor.

4.3.4.1 Maskable Interrupts

The maskable interrupt is a hardware-generated signal used by peripheral functions within the

system to get the attention of the microprocessor. Peripheral functions produce a unique INTA-D

(PCI) or IRQ0-15 (ISA) signal that is routed to interrupt processing logic that asserts the

interrupt (INTR) input to the microprocessor. The microprocessor halts execution to determine

the source of the interrupt and then services the peripheral as appropriate.

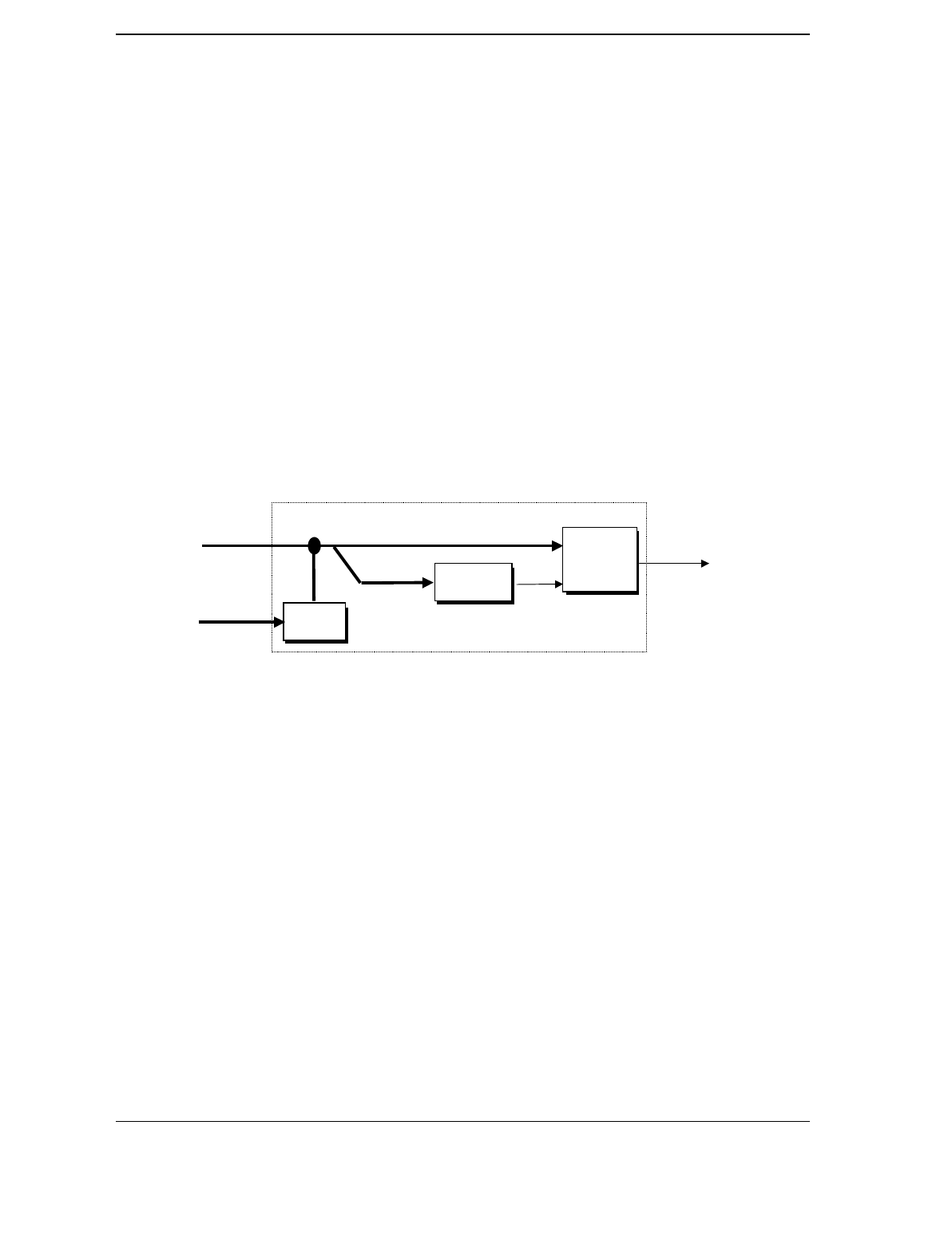

Figure 4–7.

Maskable

Interrupt Processing, Block Diagram

The South Bridge component, which includes the equivalent of two 8259 interrupt controllers

cascaded together, handles the standard AT-type (ISA) interrupt signals (IRQn). The South

Bridge also receives the PCI interrupt signals (PIRQA-..PIRQD-) from PCI devices. The PCI

interrupts can be configured by PCI Configuration Registers 55h..57h to share the standard ISA

interrupts (IRQn). The power-up default configuration has the PIRQn disabled. Table 4-11 lists

the standard source configuration for maskable interrupts and their priorities. If more than one

interrupt is pending, the highest priority (lowest number) is processed first.

Interrupt

Cntlr. 1

Interrupt

Cntlr. 2

IRQ2

IRQ1,3..7

IRQ9..12,

14,15

PCI IRQ

Routing

PIRQA-..D-

IRQ1,3..7,

9..12,

14,15

South Brid

g

e Component

INTR

Microprocessor

ISA Peripherals

& SM Functions

PCI Peripherals