Chapter 3 Processor/Memory Subsystem

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition - September 1997

3-2

Mem.

Data Bus

Mem. Addr.

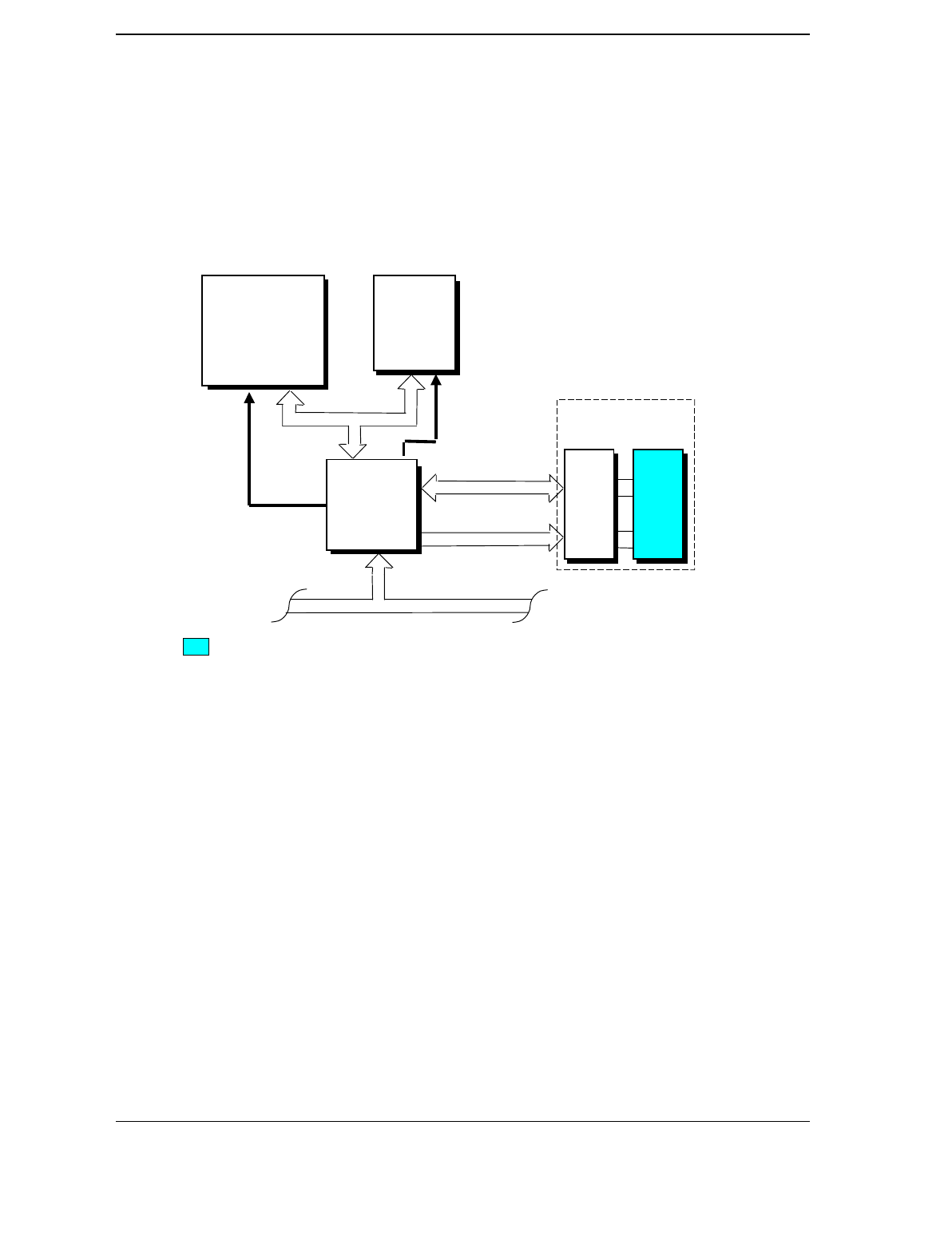

3.2 PENTIUM MMX-BASED PROCESSOR/MEMORY SUBSYSTEM

The processor/memory subsystem is based on the Pentium MMX microprocessor, a 512-KB or 1-

MB secondary cache, and a VT82C595 system controller (Figure 3-1).

Figure 3–1.

Processor/Memory Subsystem Architecture

The microprocessor is mounted in a ZIF type 7 socket that facilitates easy changing/upgrading.

The system supports both 2.8V and 3.3V core processors. Replacing the microprocessor may

require reconfiguring a DIP switch to select the correct bus frequency/core frequency

combination. Frequency selection is described in detail later in this section.

The VT82C595 system controller provides the Host/PCI bridge functions and controls transfers

with the 64-bit memory data bus. The system includes 256 kilobytes of SRAM controlled by the

system controller as a direct-mapped, write-through L2 cache to the L1 cache integrated into the

microprocessor. The system supports synchronous, pipelined burst SRAM/DRAM for the L2

cache, providing 3-1-1-1 read/write cycles at 60 and 66 MHz on a cache hit.

The standard system memory configuration consists of 16 or 32 megabytes of SDRAM system

memory. The system memory can be expanded to 256 megabytes.

Pentium MMX

Microprocessor

32-bit PCI Bus

256-KB

Secondary

Cache

Optional module

16-MB

DIMM

J7

J8

System Memory

64-Bit Host Bus

Cache/

Memory/PCI

Controller

(VT82C595)

Cntl

Cntl

Memory/PCI

Data Buffer

()

DIMM