System

Configuration

S900II

II – Instruction codes

16

01T01350_0

2.2.98

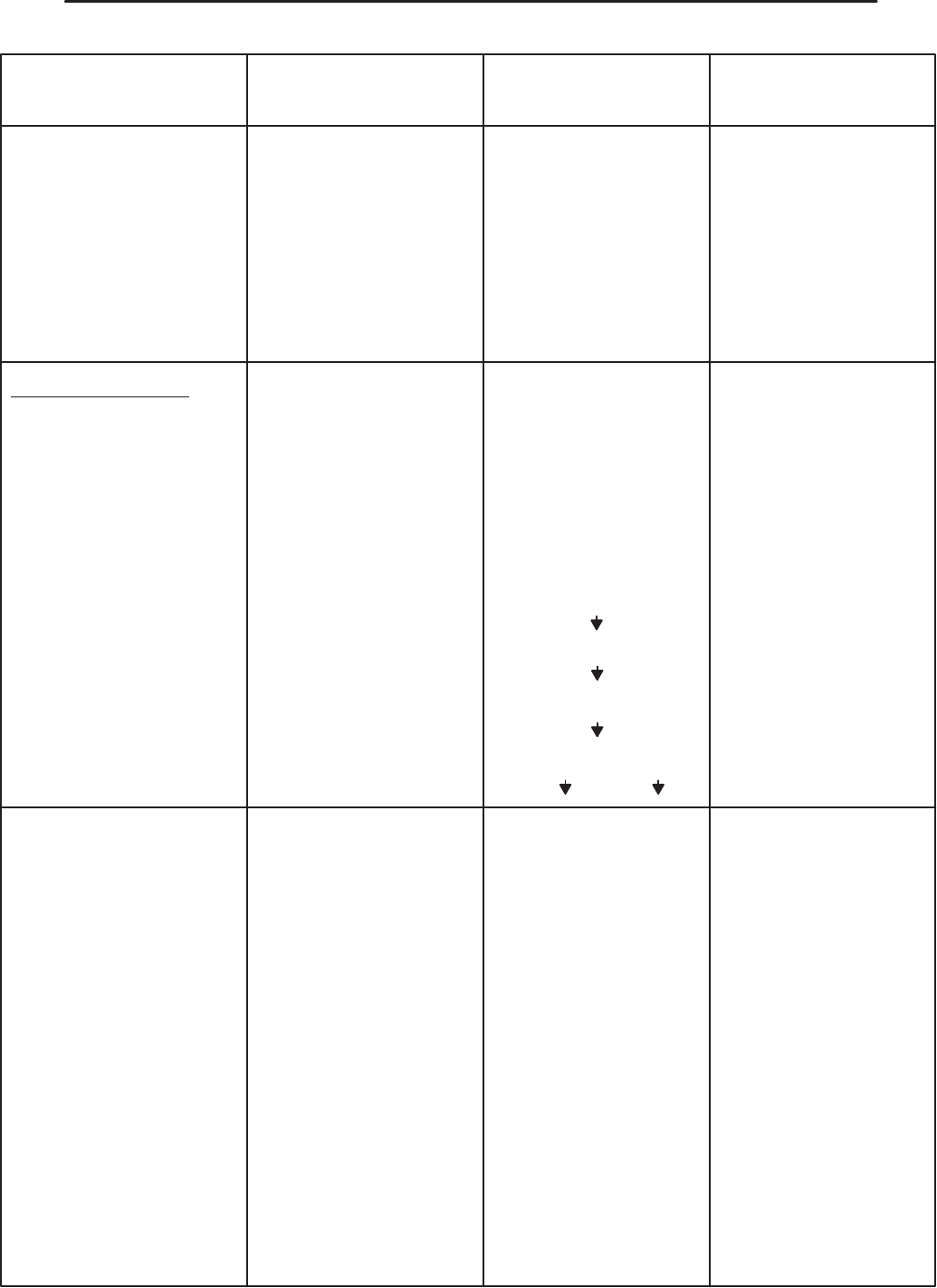

Type

of Instruction

Display Codop (hexadecimal) Examples

with Inputs (modulo 16) = IN 000 (to 112) D930 [oper. 16 bits]

> = IN 000 (to 112) D931 [oper. 16 bits]

< = IN 000 (to 112) D932 [oper. 16 bits]

AND IN 000 (to 112) D933 [oper. 16 bits]

with Word (16 bits) = WRD 0000 (to 4095) D940 [oper. 16 bits]

> = WRD 0000 (to 4095) D941 [oper. 16 bits]

< = WRD 0000 (to 4095) D942 [oper. 16 bits]

AND WRD 0000(to 4095) D943 [oper. 16 bits]

INITIALIZATION

. 1 Operand

* on Bit –> 1 SET.BIT 032 (to 127) D015 [oper. 16 bits]

on Bit –> 0 RST.BIT 032 (to 127) D017 [oper. 16 bits]

* on Output –> 1 SET.OUT 000 (to 127) D016 [oper. 16 bits]

on Output –> 0 RST.OUT 000 (to 127) D018 [oper. 16 bits]

* on Word –> 0 RST.WRD 0000 (to 4095) D019 [oper. 16 bits]

* on WWord –> 0 RST.WWRD 00 (to 63) D01D [oper. 16 bits]

* on Counter –> 0 RST.CNT 0000 (to 0015) D01A 00 [oper. 8 bits]

RST.CNT 0041 (to 9980)

D01A[oper. 8 bits] [oper. 8 bits]

. 2 Operands

* on Word (16 bits) SET.WRD 0000 (to 4095) D600 [oper. 16 bits]

–> 1st Operand

with decimal value = 0000 (to 9999) D700 [oper. 16 bits]

+ 0000 (to 9999) D701 [oper. 16 bits]

– 0000 (to 9999) D702 [oper. 16 bits]

x 0000 (to 9999) D703 [oper. 16 bits]

/ 0000 (to 9999) D704 [oper. 16 bits]

AND 0000 (to 9999) D705 [oper. 16 bits]

OR 0000 (to 9999) D706 [oper. 16 bits]

with hexadecimal value = 0000 (to FFFF) D710 [oper. 16 bits]

+ 0000 (to FFFF) D711 [oper. 16 bits]

– 0000 (to FFFF) D712 [oper. 16 bits]

x 0000 (to FFFF) D713 [oper. 16 bits]

/ 0000 (to FFFF) D714 [oper. 16 bits]

AND 0000 (to FFFF) D715 [oper. 16 bits]

OR 0000 (to FFFF) D716 [oper. 16 bits]

Variable

number

Counter number

PRG No.

SP No.

V

ariable number