Programming Details

MVME3100 Single Board Computer Installation and Use (6806800M28C)

127

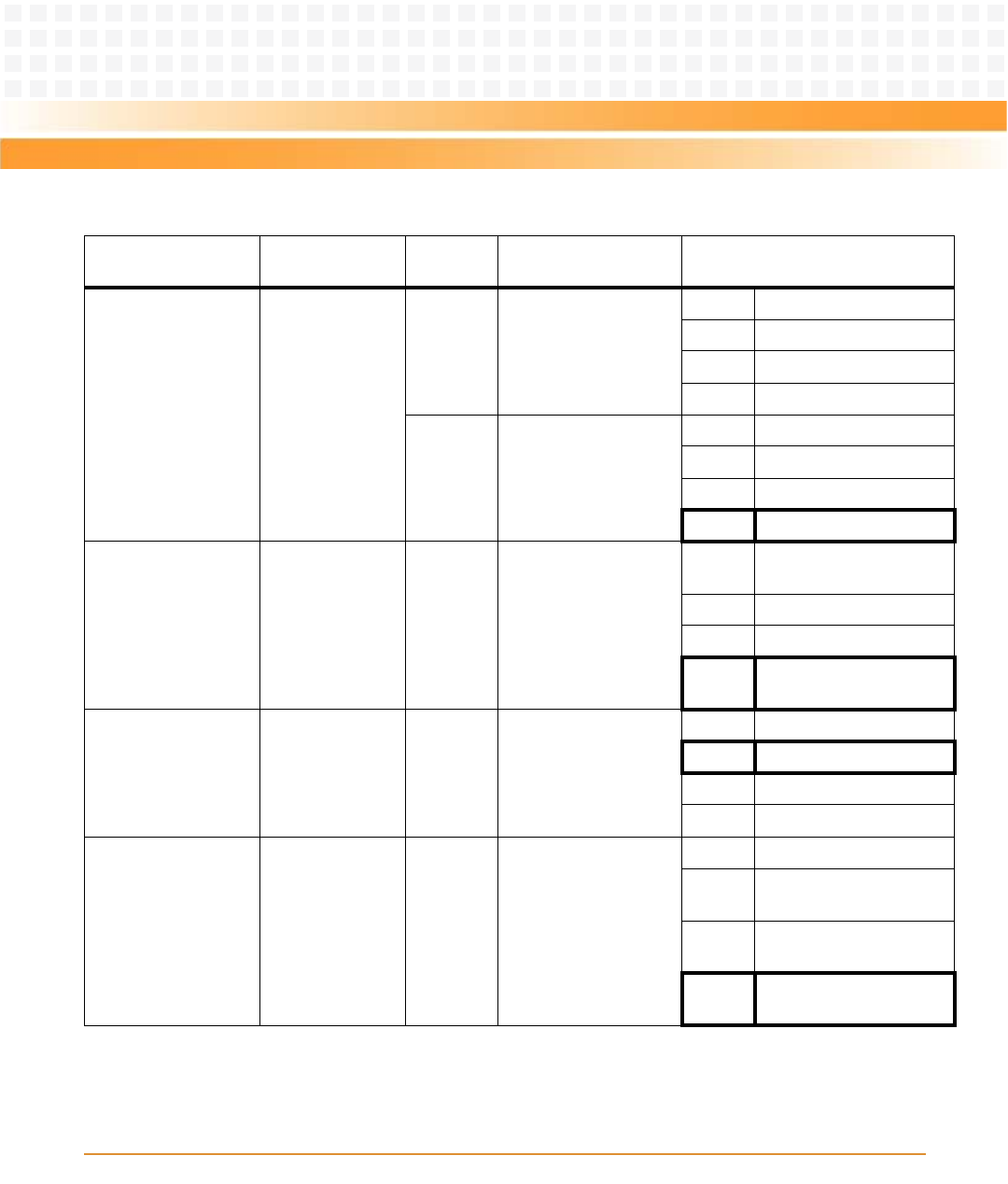

LWE [0:1] _L 4 Resistors 11 PCI Output Hold

Configuration

00 1 added buffer delay

01 0 added buffer delays

10 3 added buffer delays

11 2 added buffer delays

5

11 PCI-X Output Hold

Configuration

00 3 added buffer delays

01 2 added buffer delays

10 1 added buffer delay

11 0 added buffer delays

6

LWE [2:3] _L Resistors 11 MPC8540 Host/Agent

Configuration

00 Agent of RapidIO and

PCI/PCI-X

01 Agent of a RapidIO

10 Agent of a PCI/PCI-X

11 Host of both RapidIO and

PCI/PCI-X

LALE, LGPL2 Resistor 01 e500 Core Clock PLL

Ratio (e500 Core : CCB

Clock)

00 2:1

01 5:2

10 3:1

11 7:2

LGPL0, LGPL1 Fixed 11 RapidIO Transmit Clock

Source

00 Reserved

01 RapidIO rcv clock is

source of xmit clock

10 RapidIO xmit clock inputs

are source of xmit clock

11 CCB clock is source of

xmit clock

Table 7-1 MPC8540 Power-on Reset Configuration Settings (continued)

MPC8540 Signal Select Option

Default

Setting Description State of Bit vs Function

1