Programming Details

MVME3100 Single Board Computer Installation and Use (6806800M28C)

134

switch is ON, block B is mapped to the highest address as shown below. The MAP_SEL bit in the

Flash Control/Status register can override the switch and restore the memory map to the

normal configuration with block A selected. Upon RESET, this mapping reverts to the switch

selection.

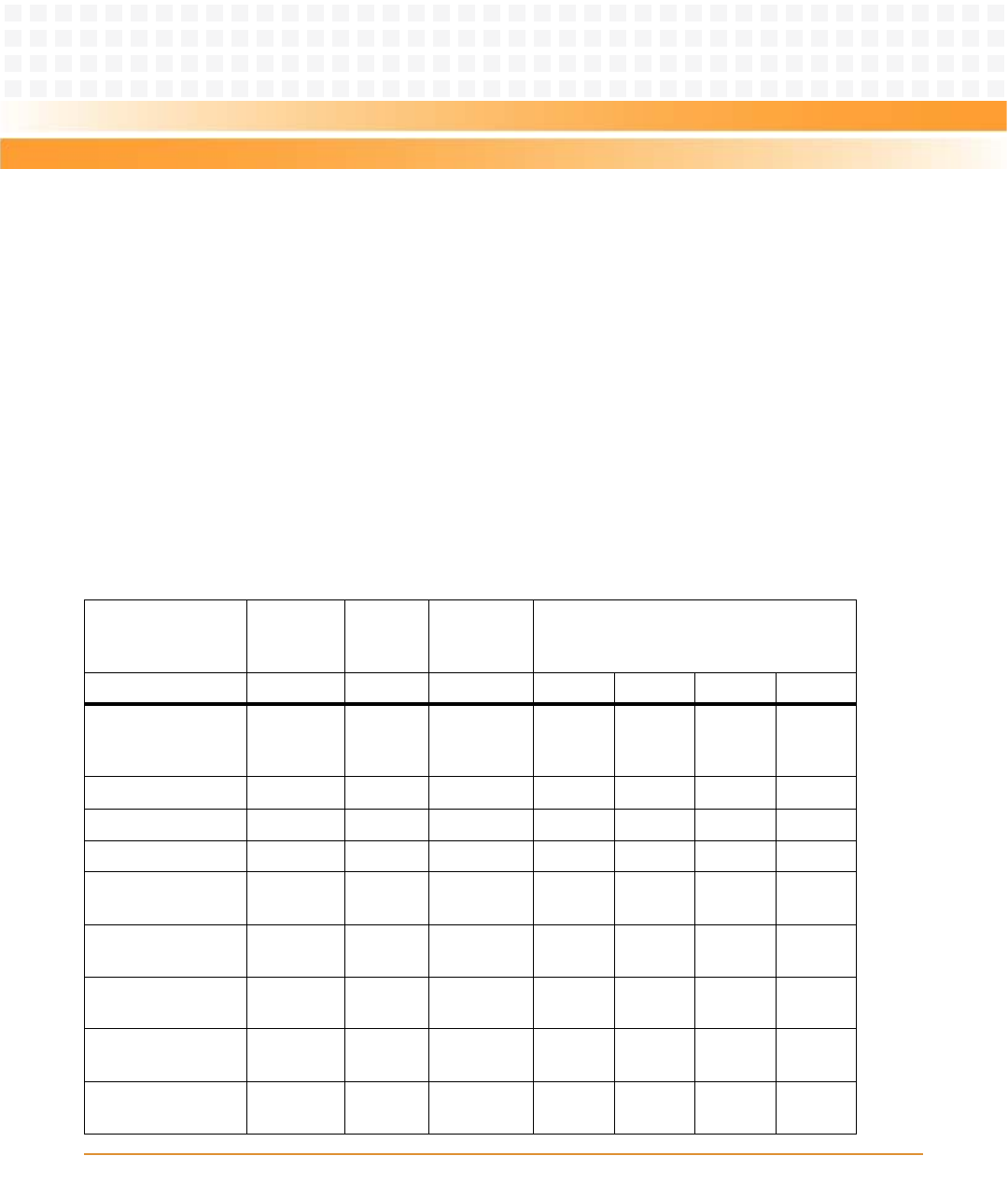

7.11 PCI IDSEL Definition

Each PCI device has an associated address line connected via a resistor to its IDSEL pin for

configuration space accesses. The following table shows the IDSEL assignments for the PCI

devices and slots on each of the PCI buses on the board, along with the corresponding interrupt

assignment to the PIC external interrupt pins. Refer to the MPC8540 Reference Manual and

PCI6520CB Data Book and for details on generating configuration cycles on each of the PCI

busses.

Table 7-7 IDSEL and Interrupt Mapping for PCI Devices

PCI Bus

Device

Number

Field

AD Line

for IDSEL

PCI Device

or Slot Device/Slot INT to MPC8540 Ext IRQ

INTA# INTB# INTC# INTD#

A

(8540) (See Note

following table)

0b0_0000 internal MPC8540

0b0_0001 17 TSi148 VME IRQ0 IRQ1 IRQ2 IRQ3

0b0_0010 18 PCI6520-1

0b0_0011 19 PCI6520-2

0b0_0100 20 Sil3124A

sATA

IRQ2

B

(PCI6520-1)

0b0_0000 16 PMC1

Primary

IRQ4 IRQ5 IRQ6 IRQ7

0b0_0001 17 PMC1

Secondary

IRQ5 IRQ6 IRQ7 IRQ4

0b0_0010 18 PMC2

Primary

IRQ6 IRQ7 IRQ4 IRQ5

0b0_0011 19 PMC2

Secondary

IRQ7 IRQ4 IRQ5 IRQ6