MVME7100 Single Board Computer Installation and Use (6806800E08A)

Functional Description Timers

70

4.6 Timers

Timing functions for the MVME7100 are provided by four global high-resolution timers

integrated into the MC864xD plus four additional independent 32-bit timers.

The four integrated 32-bit timers are clocked by the RTC input which is driven by a 1 MHz clock.

Refer to the MC864xD reference manual, listed in Appendix B, Related Documentation,

Manufacturers’ Documents on page 101 for additional details and/or programming information

The clock source for the four 32-bit timers in the PLD is 25 MHz. The timer prescaler must be

configured to generate a 1 MHz timer reference. For programming information, see MVME7100

Single Board Computer Programmer’s Reference.

4.7 Ethernet Interfaces

The MVME7100 provides four 10/100/1000 Mbps full-duplex Ethernet interfaces using the

MC864xD Ethernet Controllers. Two Broadcom BCM5482S PHYs are used. The Ethernet ports

on the MC864xD are configured to operate in RGMII mode. Two Gigabit Ethernet interfaces are

routed to front panel RJ-45 connectors with integrated LEDs for speed and activity indication.

The other two Gigabit Ethernet interfaces are routed to P2 for rear I/O. For programming

information, see MVME7100 Single Board Computer Programmer’s Reference.

4.8 Local Bus Interface

The MVME7100 uses the MC864xD Local Bus Controller (LBC) for access to on-board flash

and I/O registers. The LBC has programmable timing modes to support devices of different

access times, as well as device widths of 8, 16, and 32 bits. The MVME7100 uses the LBC in

GPCM mode to interface to two physical banks of on-board flash, an on-board Quad UART

(QUART), an MRAM, and on-board 32-bit timers along with control/status registers. Access

timing for each device type is programmable and depends on the device timing data found in

the VPD during initialization.

A hardware flash bank write protect switch is provided on the MVME7100 to enable write

protection of the NOR Flash. Regardless of the state of the software flash write protect bit in the

NOR Flash Control/Status register, write protection is enabled when this switch is ON. When

this switch is OFF, write protection is controlled by the state of the software flash write protect

bits and can only be disabled by clearing this bit in the NOR Flash Control/Status register. Note

that the F_WE_HW bit reflects the state of the switch and is only software readable whereas

the F_WP_SW bit supports both read and write operations.

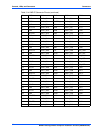

The MVME7100 provides a dual boot option for booting from one of two separate boot images

in the boot flash bank which are referred to as boot block A and boot block B. Boot blocks A and

B are each 1 MB in size and are located at the top (highest address) 2 MB of the boot flash

memory space. Block A is located at the highest 1 MB block and block B is the next highest 1

MB block. A flash boot block switch is used to select between boot block A and boot block B.

When the switch is OFF, the flash memory map is normal and block A is selected as shown in

Figure 3. When the switch is ON, block B is mapped to the highest address as shown in Figure

4. The MAP_SELECT bit in the flash Control/Status register can disable the jumper and restore

the memory map to the normal configuration with block A selected.