10-24 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

External Bus

10.3.10 Hold

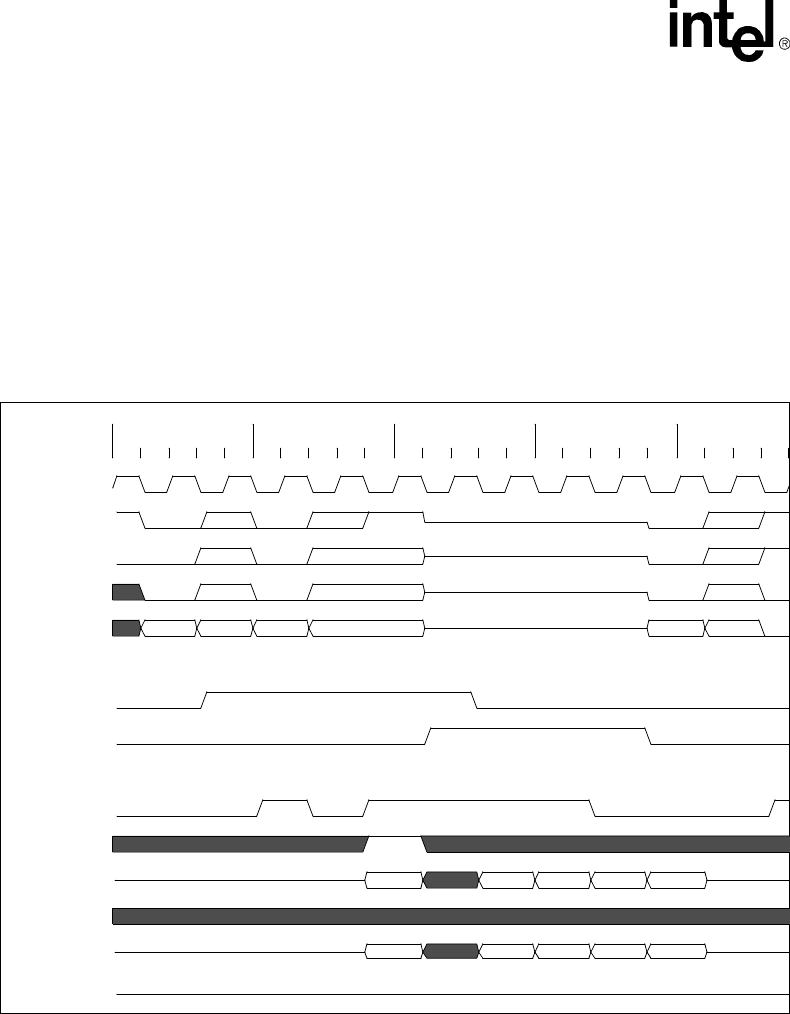

Figure 10-14 shows an example of hold being asserted to stop new transactions being issued. The

Intel

®

80200 processor floats the issue bus pins and issues no transactions until HldA is deasserted.

The Hold signal assertion does not affect the data bus, which continues to operate normally. Read

data for requests A and B continue to return.

“Rd C” shows the Intel

®

80200 processor requesting another access after Hold has been

deasserted. If Hold had continued to be asserted, another bus master could take control of the

request bus.

Figure 10-14. Hold Assertion

Rd A Rd B Rd C

0x581 0x0 0x0

Rd A Rd B0 Rd B1 Rd B2

0x0

0

0

0

1

0

1

0

1

0

0x9700x35C

Rd B3

0ns 25ns 50ns 75ns 100ns

MCLK

ADS#/LEN[2]

Lock/LEN[1]

W/R#/LEN[0]

A

Hold

HldA

DValid

CWF

D

BE#

DCB

Abort