2-12 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Programming Model

2.3.4 Event Architecture

2.3.4.1 Exception Summary

Table 2-11 shows all the exceptions that the Intel

®

80200 processor may generate, and the

attributes of each. Subsequent sections give details on each exception.

2.3.4.2 Event Priority

The Intel

®

80200 processor follows the exception priority specified in the ARM Architecture

Reference Manual. The processor has additional exceptions that might be generated while

debugging. For information on these debug exceptions, see Chapter 13, “Software Debug”.

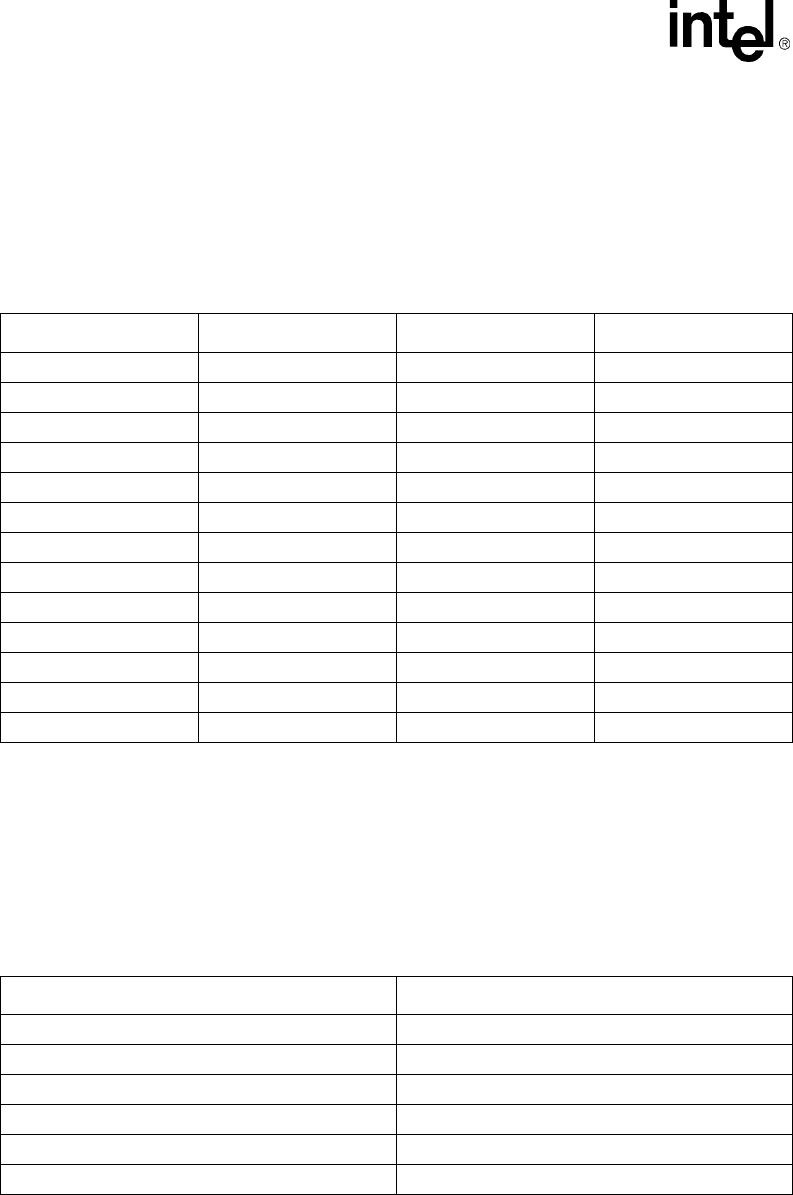

Table 2-11. Exception Summary

Exception Description Exception Type

a

a. Exception types are those described in the ARM, section 2.5.

Precise? Updates FAR?

Reset Reset N N

FIQ FIQ N N

IRQ IRQ N N

External Instruction Prefetch Y N

Instruction MMU Prefetch Y N

Instruction Cache Parity Prefetch Y N

Lock Abort Data Y N

MMU Data Data Y Y

External Data Data N N

Data Cache Parity Data N N

Software Interrupt Software Interrupt Y N

Undefined Instruction Undefined Instruction Y N

Debug Events

b

b. Refer to Chapter 13, “Software Debug” for more details

varies varies N

Table 2-12. Event Priority

Exception Priority

Reset 1 (Highest)

Data Abort (Precise & Imprecise) 2

FIQ 3

IRQ 4

Prefetch Abort 5

Undefined Instruction, SWI 6 (Lowest)