Developer’s Manual March, 2003 B-3

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Optimization Guide

B.2.1.2. Intel

®

80200 Processor Pipeline Organization

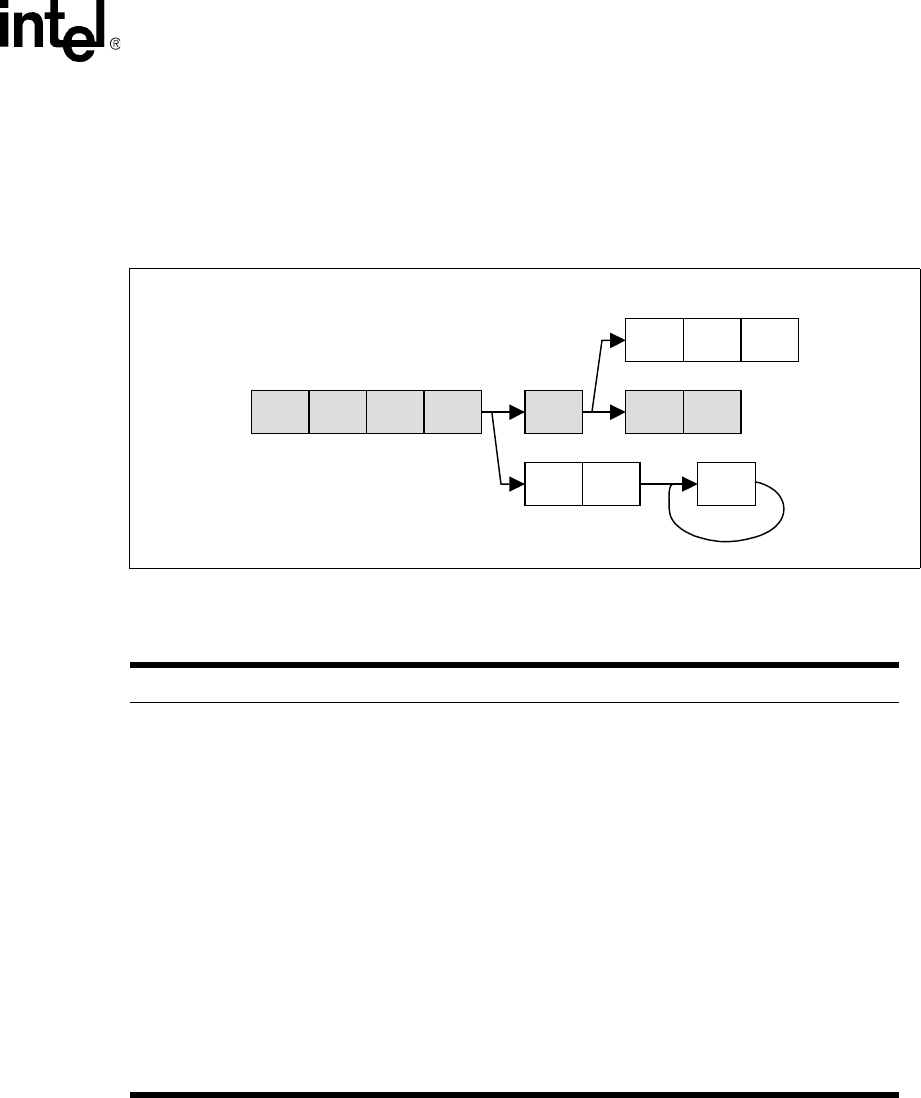

The Intel

®

80200 processor single-issue superpipeline consists of a main execution pipeline, MAC

pipeline, and a memory access pipeline. These are shown in Figure B-1, with the main execution

pipeline shaded.

Table B-1 gives a brief description of each pipe-stage.

Figure B-1. Intel

®

80200 Processor RISC Superpipeline

F1 F2 ID RF X1 X2

XWB

M1 M2 Mx

D1 D2

DWB

Main execution pipeline

MAC pipeline

Memory pipeline

Table B-1. Pipelines and Pipe stages

Pipe / Pipestage Description Covered In

Main Execution Pipeline

Handles data processing instructions

Section B.2.3

IF1/IF2 Instruction Fetch “

ID Instruction Decode “

RF Register File / Operand Shifter “

X1 ALU Execute “

X2 State Execute “

XWB Write-back “

Memory Pipeline Handles load/store instructions Section B.2.4

D1/D2 Data Cache Access “

DWB Data cache writeback “

MAC Pipeline Handles all multiply instructions Section B.2.5

M1-M5 Multiplier stages “

MWB (not shown) MAC write-back - may occur during M2-M5 “