12-4 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Performance Monitoring

12.4 Performance Monitor Control Register (PMNC)

The performance monitor control register (PMNC) is a coprocessor register that:

• controls which events PMN0 and PMN1 monitors

• detects which counter overflowed

• enables/disables interrupt reporting

• extends CCNT counting by six more bits (cycles between counter rollover = 2

38

)

• resets all counters to zero

• and enables the entire mechanism

Table 12-3 shows the format of the PMNC register.

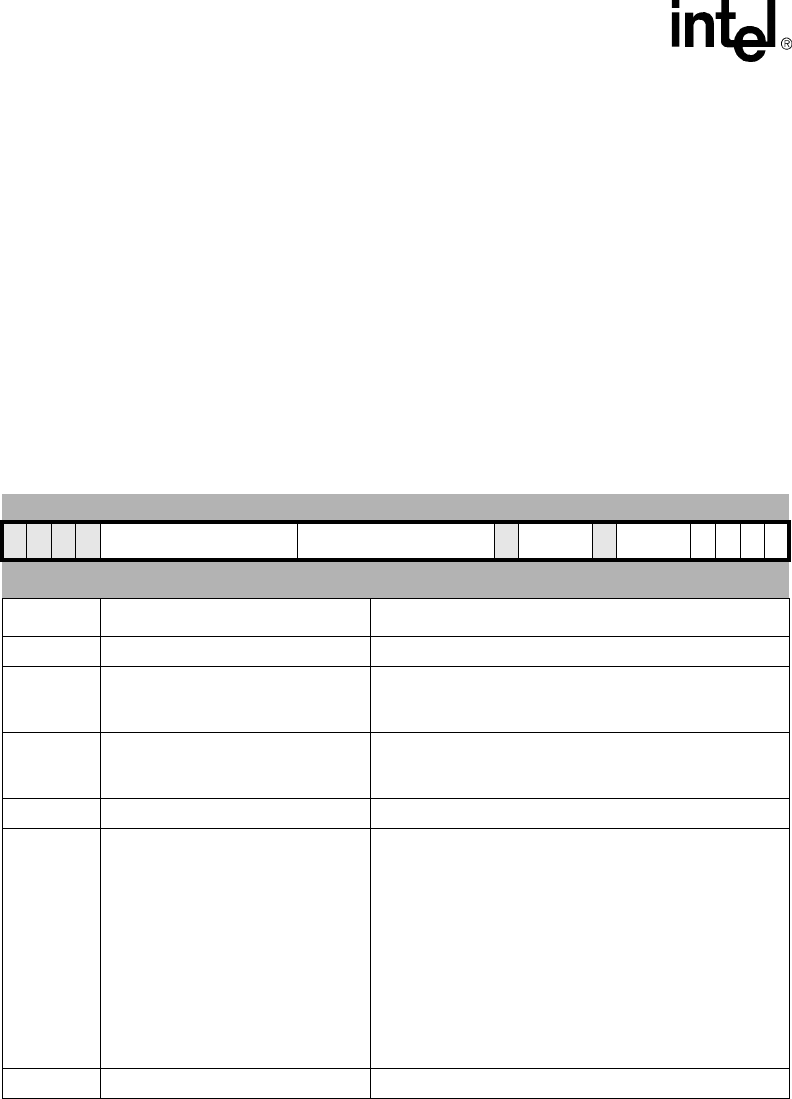

Table 12-3. Performance Monitor Control Register (CP14, register 0) (Sheet 1 of 2)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

evtCount1 evtCount0 flag inten D C P E

reset value: E and inten are 0, others unpredictable

Bits Access Description

31:28 Read-unpredictable / Write-as-0 Reserved

27:20 Read / Write

Event Count1 - identifies the source of events that

PMN1 counts. See Table 12-4 for a description of the

values this field may contain.

19:12 Read / Write

Event Count0 - identifies the source of events that

PMN0 counts. See Table 12-4 for a description of the

values this field may contain.

11 Read-unpredictable / Write-as-0 Reserved

10:8 Read / Write

Overflow/Interrupt Flag - identifies which counter

overflowed

Bit 10 = clock counter overflow flag

Bit 9 = performance counter 1 overflow flag

Bit 8 = performance counter 0 overflow flag

Read Values:

0 = no overflow

1 = overflow has occurred

Write Values:

0 = no change

1 = clear this bit

7 Read-unpredictable / Write-as-0 Reserved