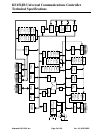

KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 1 of 120 Ver. 0.9 KS152JB2

1.0 INTRODUCTION

The 80C152 Universal Communications Controller is an 8-bit microcontroller designed for the

intelligent management of peripheral systems or components. The 80C152 is a derivative of the

80C51 and retains the same functionality. These enhancements include: a high speed multi-proto-

col serial communication interface, two channels for DMA transfers, HOLD/HLDA bus control, a

fifth I/O port, expanded data memory, and expanded program memory.

In addition to a standard UART, referred to here as Local Serial Channel (LSC), the 80C152 has

an on-board multi-protocol communication controller called the Global Serial Channel (GSC).

The GSC interface supports SDLC, CSMA/CD, user definable protocols, and a subset of HDLC

protocols. The GSC capabilities include: address recognition, collision resolution, CRC genera-

tion, flag generation, automatic retransmission, and a hardware based acknowledge feature. This

high speed serial channel is capable of implementing the Data Link Layer and the Physical Link

Layer as shown in the OSI open systems communication model. This model can be found in the

document “Reference Model for Open Systems Interconnection Architecture”, ISO/TC97/SC16

N309.

The DMA circuitry consists of two 8-bit DMA channels with 16-bit addressability. The control

signals; Read (RD), Write (WR), hold and hold acknowledge (HOLD/HLDA) are used to access

external memory. The DMA channels are capable of addressing up to 64K bytes (16 bits). The

destination or source address can be automatically incremented. The lower 8 bits of the address

can be automatically incremented. The lower 8 bits of the address are multiplexed on the data bus

Port 0 and the upper eight bits of address will be on Port 2. Data is transmitted over an 8-bit

address/data bus. Up to 64k bytes of data may be transmitted for each DMA activation.

The new I/O port (P4) function the same as Ports 1-3 found on the 80C51.

Internal memory has been doubled in the 80C152. Data memory has been expanded to 256 bytes,

and internal program memory has been expanded to 8 bytes.

There are also some specific differences between the 80C152 and the 80C51. The first difference

is that RESET is active low in the 80C152 and active high in the 80C51H. The second difference

is that GF0 and GF1, general purpose flags in PCON, have been renamed GFIEN and XRCLK.

GFIEN enables idle flags to be generated in SDLC mode, and XRCLK enables the receiver to be

externally clocked. All of the previously unused bits are now being used and interrupt vectors

have been added to support the new enhancements.

Throughout the rest of this manual the 80C152 will be referred to generically as the “C152”. The

C152 is based on the 80C51 architecture and utilizes the same 80C51 instruction set. There have

been no new instructions added. All the new features and peripherals are supported by an exten-

sion of the Special Function Registers (SFRs). A brief information on cpu functions as: the

instruction set, port operation, timer/counters, etc., is included in this document.