KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 83 of 120 Ver. 0.9 KS152JB2

The functions of the ARB and REQ bits in PCON, then, are

4.3.3 USING THE HOLD/HLDA ACKNOWLEDGE

The

HOLD/HOLDA logic only affects DMA operation with external RAM and don’t affect other

operations with external RAM, such as MOVX instruction.

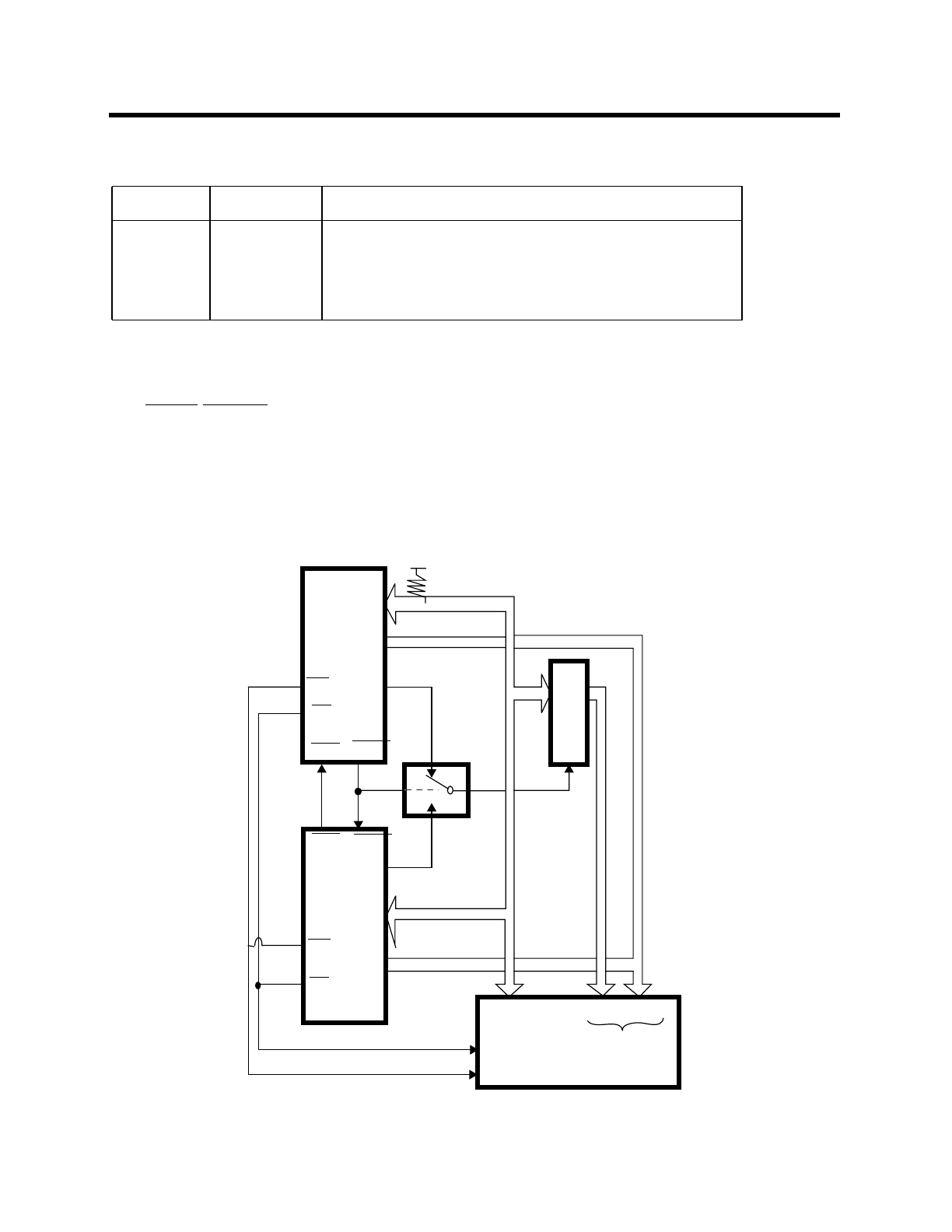

Figure shows a system in which two 83C152s are sharing a global RAM. In this system, both

CPUs are executing from internal ROM. Neither CPU uses the bus except to access the shared

RAM, and such accesses are done only through DMA operations, not by MOVX instructions.

Two 83C152s Sharing External RAM

One CPU is programmed to be the Arbiter and the other, to be the Requester. The ALE Switch

ARB REQ Hold/Hold Acknowledge Logic

0

0

1

1

0

1

0

1

Disabled

C152 generates HLD, detects HLDA

C152 detects HLD, generates HLDA

Invalid

83C152

ARB

WR

RD

P2

P0

ALE

HLD

HLDA

8 X 10 kohms

7

4

L

S

3

7

3

ALE SWITCH

DATA

LOW HIGH

SHARED RAM

OE

WE

HLD

HLDA

ALE

83C152

REQ

WR

RD

P0

P2

ADDR