KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 36 of 120 Ver. 0.9 KS152JB2

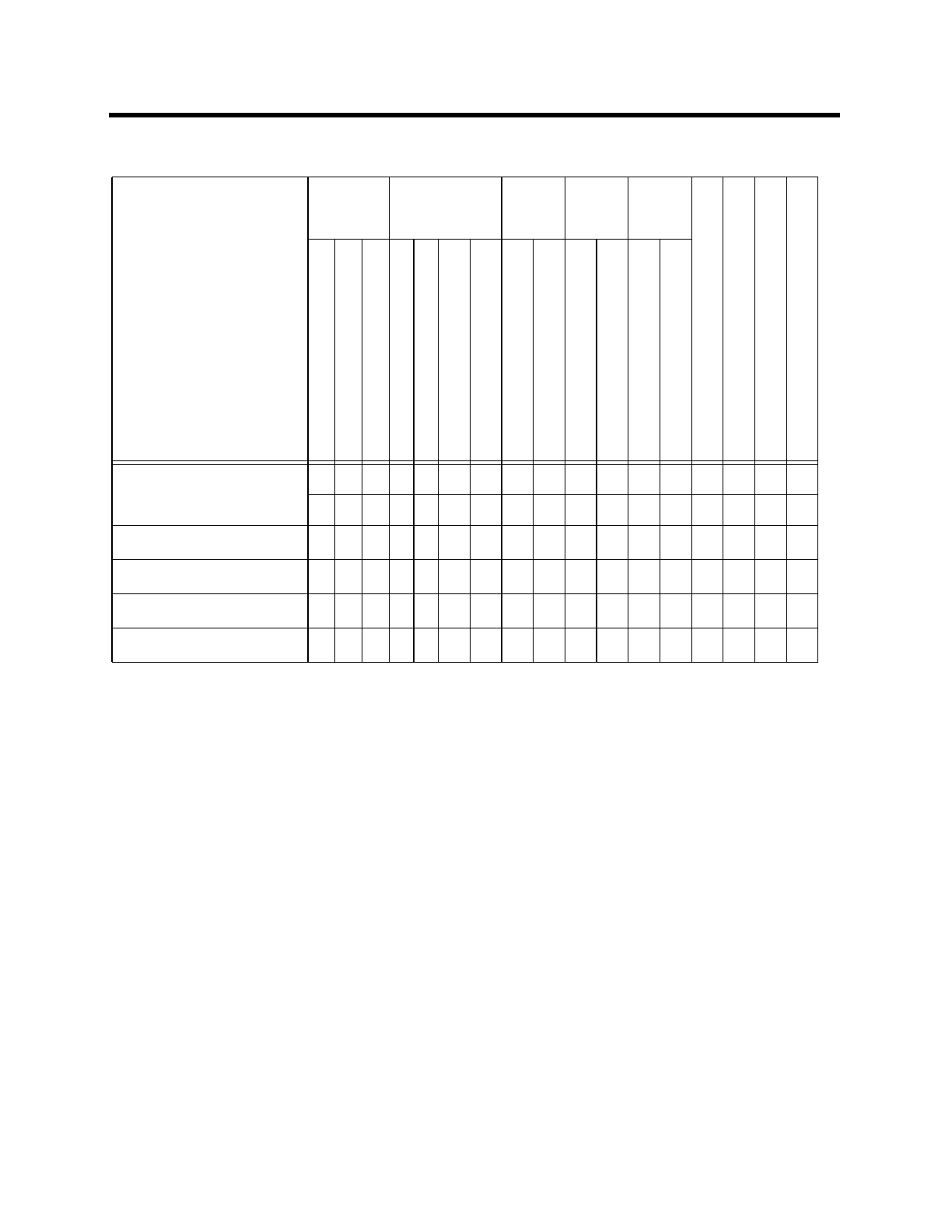

Note 1: Programmable in Raw transmit or receive mode.

Almost all the options available from Table can be implemented with the proper software to per-

form the functions that are necessary for the options selected. In Table 3.1, a judgment has been

made by the authors on which options are practical and which are not. What this means is that in

table , an “N” should be interpreted as meaning that the option is either not practical when imple-

mented with user software or that it cannot be done. An “O” is used when that function is one of

several that can be implement with the GSC without additional user software.

The GSC is targeted to operate at bit rates up to 2.4 Mbps using the external clock options and up

to 2 MBps using the internal baud rate generator, internal data formatting and on-chip clock

recovery. The baud rate generator allows most standard rates to be achieved. These standards

include the proposed IEEE802.3 LAN standard(1.0MBps) and the T1 standard (1.544Mbps). The

baud rate is derived from the crystal frequency. This makes crystal selection important when

determining the frequency and accuracy of the baud rate.

The user needs to be aware that after reset, the GSC is in CSMA/CD mode, IFS = 256 bit times,

and a bit time equals 8 oscillator periods. The GSC will remain in this mode until the interframe

space expires. If the user changes to SDLC mode or the parameters used in CSMA/CD, these

changes will not take effect until the interframe space expires. A requirement for the interframe

space timer to begin is that the receiver be in an idle state. This makes it possible for the GSC to

Control cpu

Control dma

OOO

OOOOOOOOXNOOOO

OOO

OOOOOOOONXOOOO

Raw Receive

OOO

111 1 OO1 1 1 1 XN1 1

Raw Transmit

NNN

111 1 NN1 1 1 1 NX1 1

CSMA

OOO

NOOOOONOOOOOXN

SDLC

NNN

POOONNOOOOOONX

Table 10:

N-Not available.

M-Mandatory.

O-Optional.

P-Normally Preferred

X-N/A

backoff

preamble Jam Clock

contr

ol

r

a

w

tr

a

n

s

m

it

r

a

w

r

e

c

e

i

v

e

c

s

m

a

/

c

d

s

d

l

c

n

o

r

m

a

l

a

lt

e

r

n

a

t

e

d

e

t

e

r

m

i

n

i

s

ti

c

n

o

n

e

8

b

i

t

3

2

b

it

6

4

b

it

d

c

c

r

c

/

e

x

t

e

r

n

a

l

i

n

t

e

r

n

a

l

c

p

u

d

m

a