KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 72 of 120 Ver. 0.9 KS152JB2

PCON.3(XRCLK) -GSC External Receive Clock Enable- Writing a 1 to XRCLK enables an

external clock to be applied to pin 5(Port 1.4). The external clock is used to determine when bits

are loaded into the receiver.

PCON.4 (GAREN) - GSC Auxiliary Receiver Enable Bit - This bit needs to be set to a 1 to enable

the reception of back-to-back SDLC frames. A back-to-back SDLC frame is when the EOF and

BOF is shared between two sequential frames intended for the same station on the link. If

GAREN contains a 0 then the receiver will be disabled upon reception of the EOF and by the time

user software re-enables the receiver the first bit(s) may have already passed, in the case of back-

to-back frames. Setting GAREN to a 1, prevents the receiver from being disabled by the EOF but

GREN will be cleared and can be checked by user software to determine that an EOF has been

received. GAREN has no effect if the GSC is in CSMA/CD mode.

PRBS (0E4H) - Pseudo-Random Binary Sequence - This register contains a pseudo-random num-

ber to be used in the CSMA/CD backoff algorithm. The number is generated by using a feedback

shift register clocked by the CPU phase clocks. Writing all ones to the PRBS will freeze the value

at all ones. Writing any other value to it will restart the PRBS generator.The PRBS is initialized to

all zero’s during RESET. A read of location 0E4H will not necessary give the seed used in the

backoff algorithm because the PRBS may have been altered between the time when the seed was

generated and before a READ has been internally executed.

RFIFO (0F4H) - Receive FIFO - RFIFO is a 3 byte buffer that is loaded each time the GSC

receiver has a byte of data. Associated with RFIFO is a pointer that is automatically updated with

each read of the FIFO. A read of RFIFO fetches the oldest data in the FIFO.

RSTAT.0 (HABEN) - Hardware Based Acknowledge Enable - If set, enables the hardware based

acknowledge feature. The user software is responsible for setting or clearing this flag.

RSTAT.1 (GREN) - Receiver Enable -When set, the receiver is enabled to accept incoming

frames. The user must clear RFIFO with software before enabling the receiver. RFIFO is cleared

by reading the contents of RFIFO until RFIFO=0. After each read of RFIFO, it takes one machine

cycle for the status of RFNE to be updated. Setting GREN is cleared by hardware at the end of a

reception or if any receive errors are detected. The user software is responsible for setting this flag

and the GSC or user software can clear it. The status of GREN has no effect on whether the

receiver input circuitry always monitors the receive pin.

RSTAT.2 (RFNE) - Receive FIFO Not Empty - If set, indicates that the receive FIFO contains

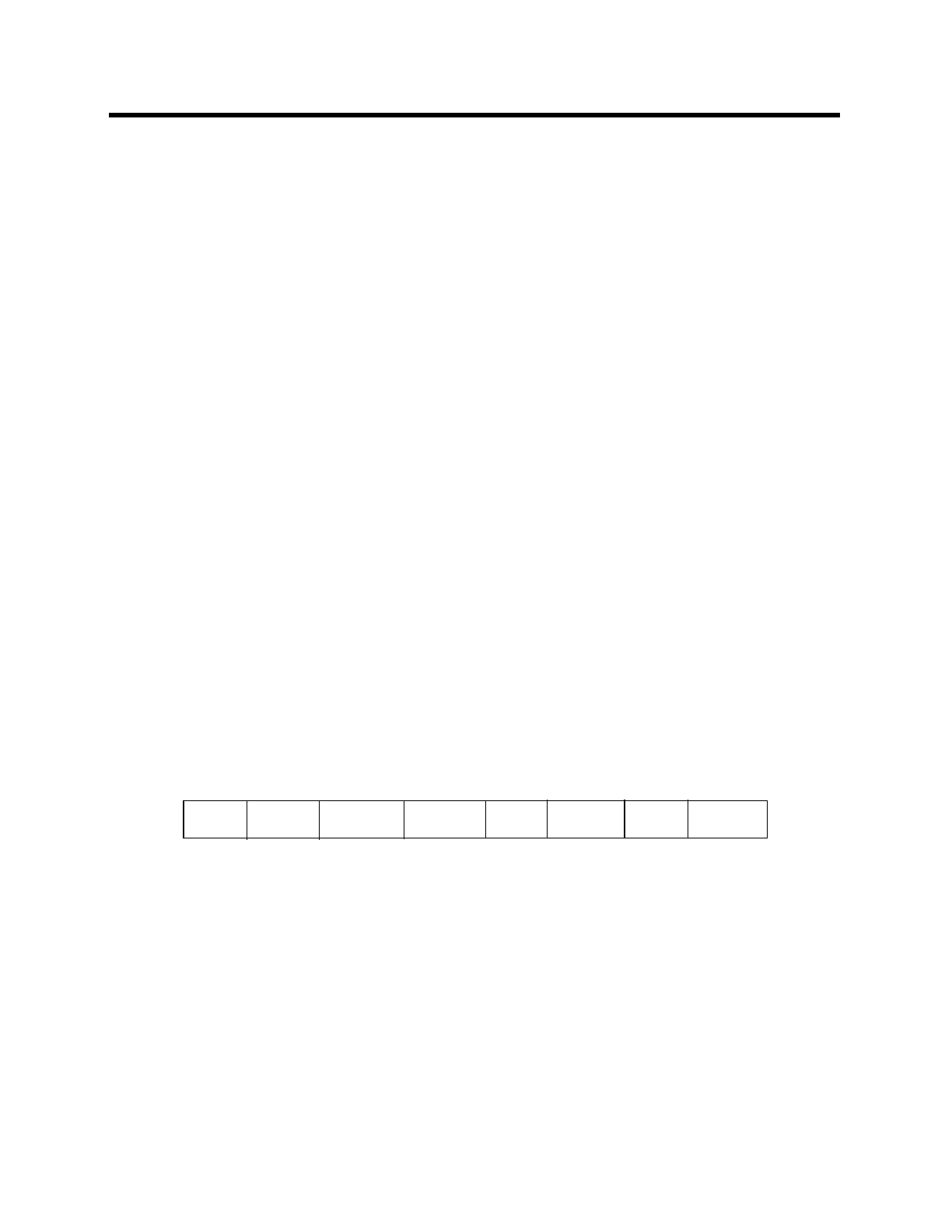

OR

RCABT

AE CRCE RDN RFNE GREN HABEN

7

6

5

4

32

1

0

RSTAT (0E8H) - Receive Status Register