KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 106 of 120 Ver. 0.9 KS152JB2

MYSLOT.7 (DCJ) - Determines the type of Jam used during CSMA/CD operation when a collision

occurs. If set to a 1 then a low D.C level is used as the jam signal. If cleared, then

CRC is used as

the jam signal. The jam is applied for a length of time equal to the CRC length.

NOACK - No Acknowledgment error bit, see TSTAT.

NRZI - Non-Return to Zero Inverted, a type of data encoding where a 0 is represented by a change

in the level of the serial link. A 1 is represented by no change.

OVR - Overrun Error bit, see RSTAT.

PR - Protocol select bit, see GMOD.

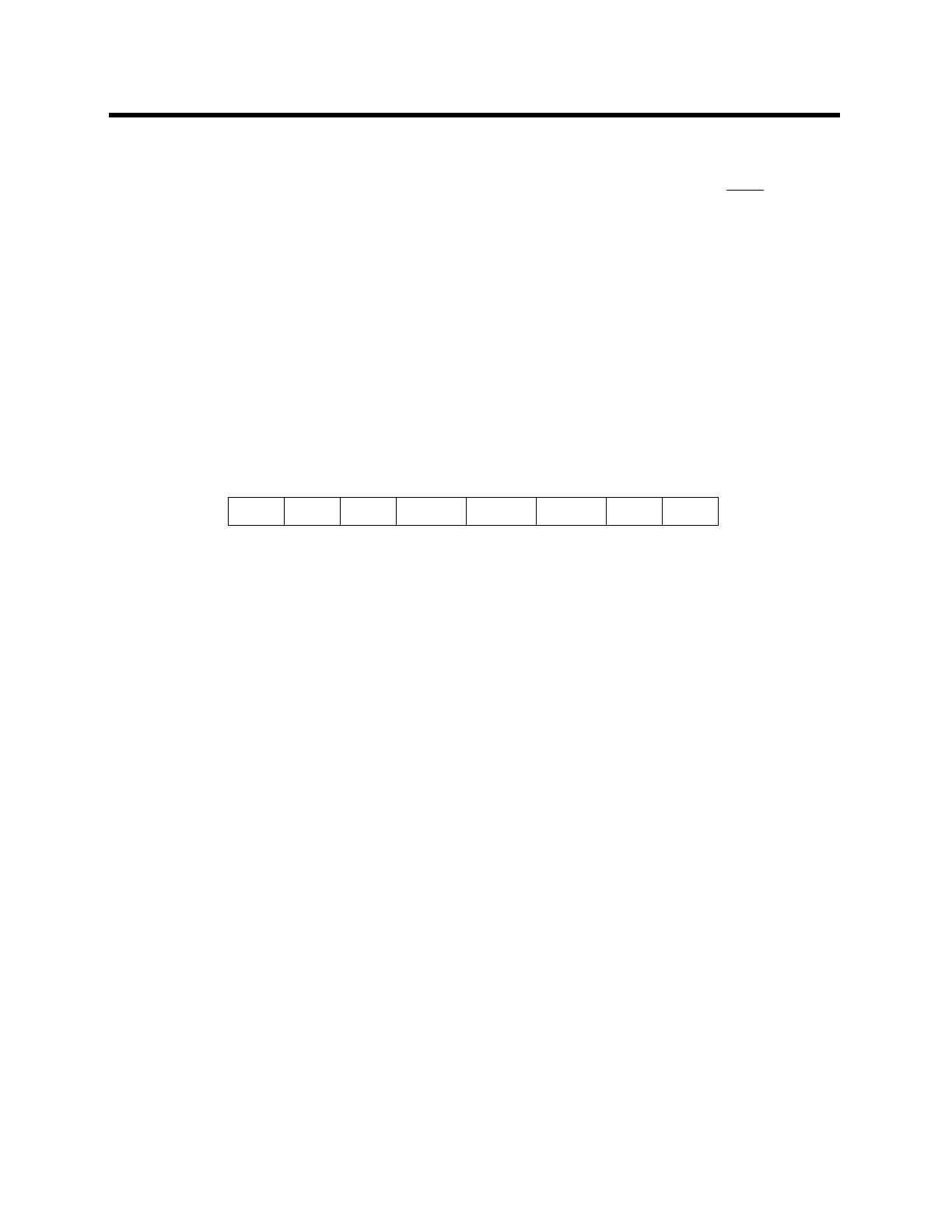

PCON (87H)

PCON.0 (IDL) - Idle bit, used to place the C152 into the idle power saving mode.

PCON.1 (PD) - Power Down bit, used to place the C152 into the power down power saving mode.

PCON.2 (GFIEN) - GSC Flag Idle Enable bit, when set, enables idle flags (01111110) to be gen-

erated between transmitted frames in SDLC mode.

PCON.3 (XRCLK) - External Receive Clock bit, used to enable an external clock to be used for

only the receiver portion of the GSC.

PCON.4 (GAREN) - GSC Auxiliary Receive Enable bit, used to enable the GSC to receive back-

to-back SDLC frames. This bit has no effect in CSMA/CD mode.

PCON.5 (REQ) - Requester mode bit, set to a 1 when C152 is to be operated as the requester station

during DMA transfers.

PCON.6 (ARB) - Arbiter mode bit, set to a 1 when C152 is to be operated as the arbiter during

DMA transfers.

PCON.7 (SMOD) - LSC mode bit, used to double the baud rate on the LSC.

PDMA0 - Priority bit for DMA Channel 0 interrupt, see IPN1.

PDMA1 - Priority bit for DMA Channel 1 interrupt, see IPN1.

PGSRE - Priority bit for GSC Receive Error interrupt, see IPN1.

01234567

GAREN XRCLK GFIEN PD IDLREQARBSMOD