KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 51 of 120 Ver. 0.9 KS152JB2

that the correct remainder is left. The remainder that is checked for is 001110100001111B (1D0F

Hex). If there is a mismatch, an error is generated. The user software has the option of enabling

this interrupt so the CPU is notified.

16-Bit CRC

EOF - The End Of Frame (EOF) indicates when the transmission is complete. The EOF is identi-

fied by the end flag. An end flag consists of the bit pattern 01111110, The EOF can also serve as

the BOF for the next frame.

3.3.3 DATA ENCODING

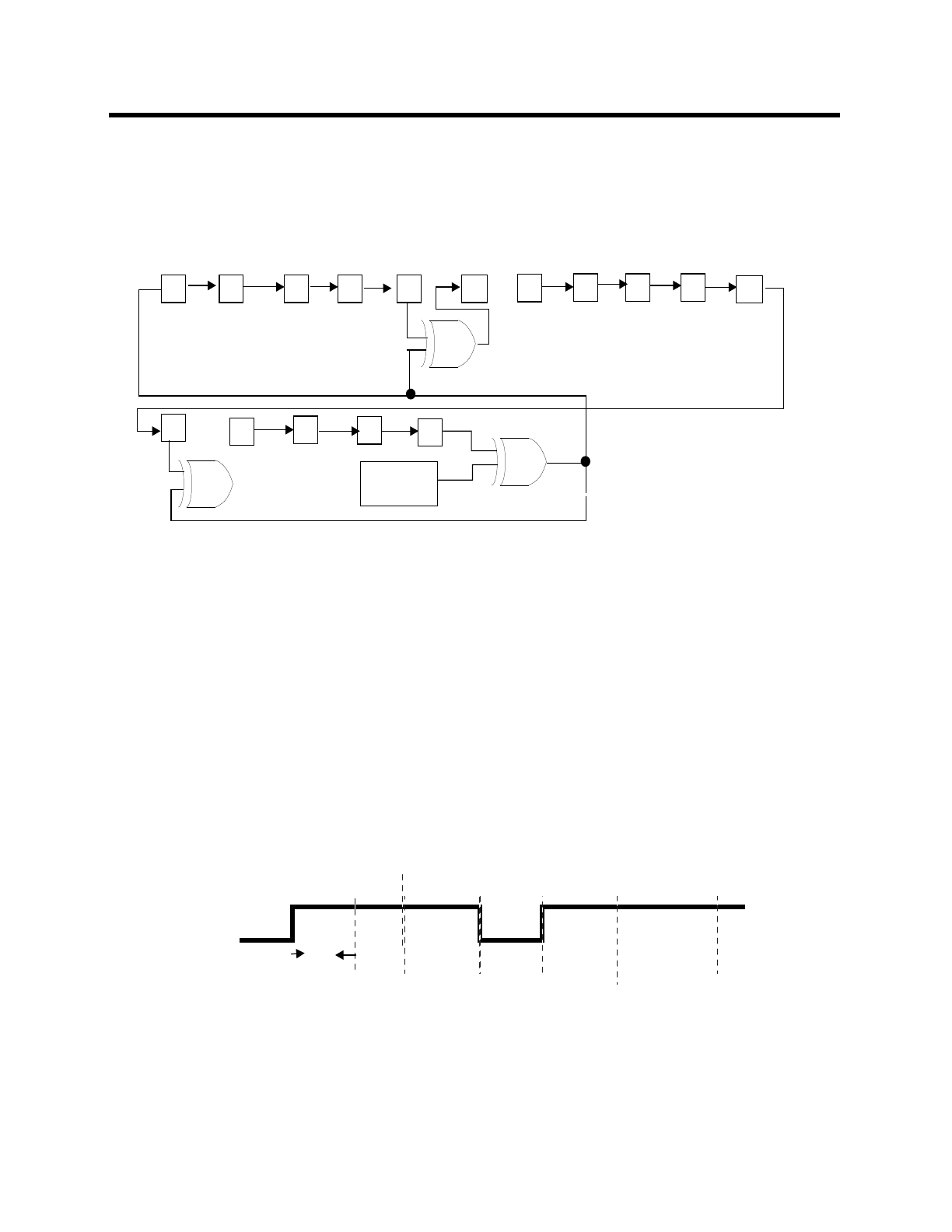

The transmission of data in SDLC mode is done via NRZI encoding as shown in Figure below.

NRZI encoding transmits data by changing the state of the output whenever a 0 is being transmit-

ted. Whenever a 1 is transmitted the state of the output remains the same as the previous bit and

remains valid for the entire bit time. When SDLC mode is selected it automatically enables the

NRZI encoding on the transmit line and NRZI decoding on the receive line. The Address and Info

bytes are transmitted LSB first. The Address and Info bytes are transmitted LSB first. The CRC is

transmitted MSB first.

3.3.4 BIT STUFFING/STRIPPING

In SDLC mode one of the primary rules of the protocol is that in any normal data transmission,

there will never be an occurrence of more than 5 consecutive 1s. The GSC takes care of this

housekeeping chore by automatically inserting a 0 after every occurrence of 5 consecutive 1s and

the receiver automatically removes a zero after receiving 5 consecutive 1s. All the necessary steps

1

2

34 5

6789

100

11

12

13

14 15

RECEIVED

BIT

0

1

1

0

0

1

NRZI

BIT

TIME