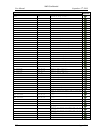

AMD Confidential

User Manual September 12

th

, 2008

Appendix A 209

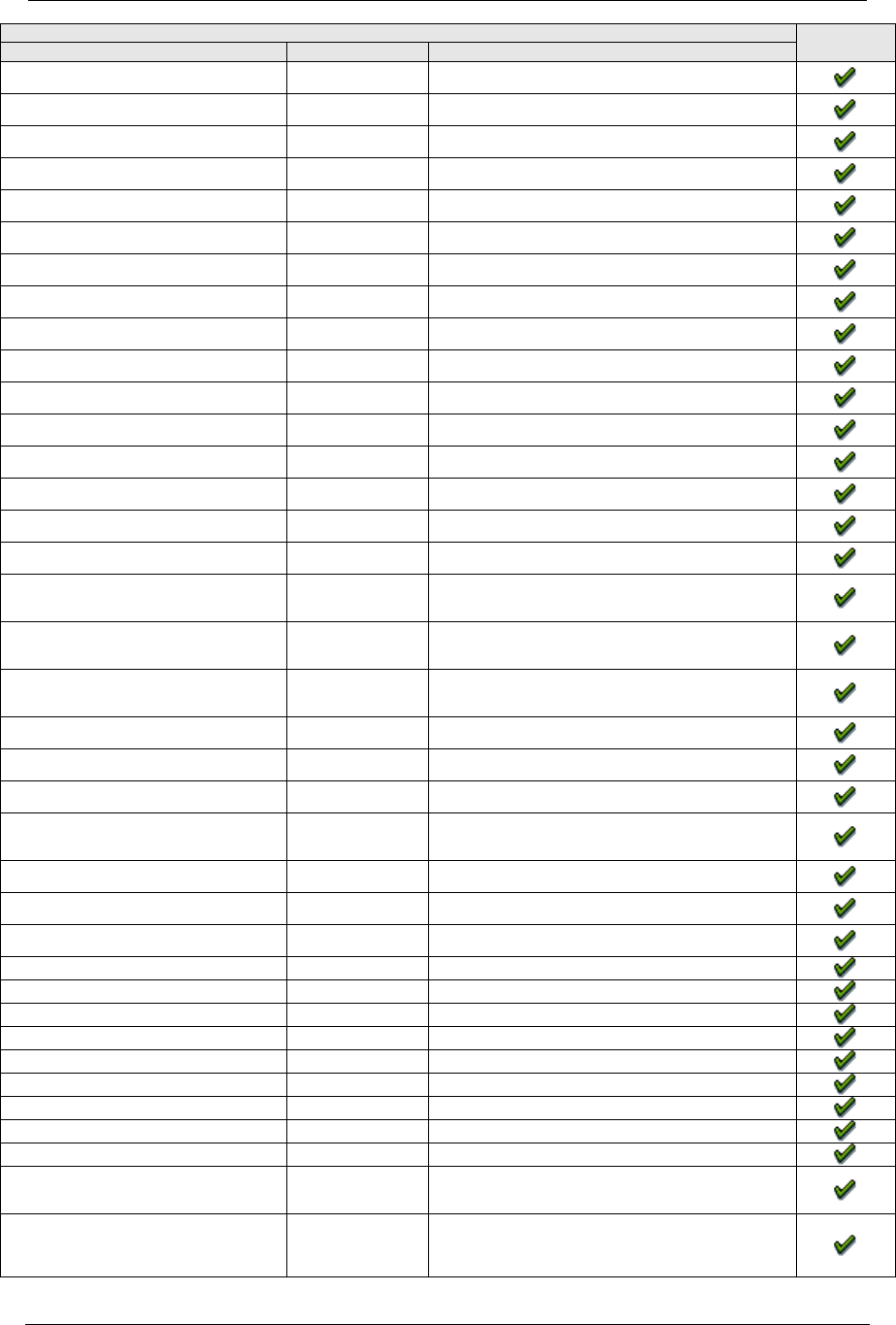

Instruction

Supported

Mnemonic

Opcode

Description

POP DS

1F

Pop the top of the stack into the DS

register.

POP ES

07

Pop the top of the stack into the ES

register.

POP SS

17

Pop the top of the stack into the SS

register.

POP FS

0F A1

Pop the top of the stack into the FS

register.

POP GS

0F A9

Pop the top of the stack into the GS

register.

POPA

61

Pop the DI, SI, BP, SP, BX, DX, CX,

and AX registers.

POPAD

61

Pop the EDI, ESI, EBP, ESP, EBX, EDX,

ECX, and EAX registers.

POPF

9D

Pop a word from the stack into the

FLAGS register.

POPFD

9D

Pop a doubleword from the stack into

the EFLAGS register.

POPFQ

9D

Pop a quadword from the stack into

the RFLAGS register.

PREFETCH mem8

0F 0D /0

Prefetch processor cache line into L1

data cache.

PREFETCHW mem8

0F 0D /1

Prefetch processor cache line into L1

data cache and mark it modified.

PREFETCHNTA mem8

0F 18 /0

Move data closer to the processor

using the NTA reference.

PREFETCHT0 mem8

0F 18 /1

Move data closer to the processor

using the T0 reference.

PREFETCHT1 mem8

0F 18 /2

Move data closer to the processor

using the T1 reference.

PREFETCHT2 mem8

0F 18 /3

Move data closer to the processor

using the T2 reference.

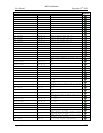

PUSH reg/mem16

FF /6

Push the contents of a 16-bit

register or memory operand onto the

stack.

PUSH reg/mem32

FF /6

Push the contents of a 32-bit

register or memory operand onto the

stack.

PUSH reg/mem64

FF /6

Push the contents of a 64-bit

register or memory operand onto the

stack.

PUSH reg16

50 +rw

Push the contents of a 16-bit

register onto the stack.

PUSH reg32

50 +rd

Push the contents of a 32-bit

register onto the stack.

PUSH reg64

50 +rq

Push the contents of a 64-bit

register onto the stack.

PUSH imm8

6A

Push an 8-bit immediate value (sign-

extended to 16, 32, or 64 bits) onto

the stack.

PUSH imm16

68

Push a 16-=bit immediate value onto

the stack.

PUSH imm32

68

Push the contents of a 32-bit

register onto the stack.

PUSH imm64

68

Push the contents of a 64-bit

register onto the stack.

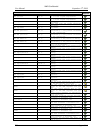

PUSH CS

0E

Push the CS selector onto the stack.

PUSH SS

16

Push the SS selector onto the stack.

PUSH DS

1E

Push the DS selector onto the stack.

PUSH ES

06

Push the ES selector onto the stack.

PUSH FS

0F A0

Push the FS selector onto the stack.

PUSH GS

0F A8

Push the GS selector onto the stack.

PUSHF

9C

Push the FLAGS word onto the stack.

PUSHFD

9C

Push the EFLAGS word onto the stack.

PUSHFQ

9C

Push the RFLAGS word onto the stack.

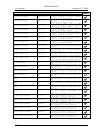

RCL reg/mem8,1

D0 /2

Rotate the 9 bits consisting of the

carry flag and an 8-bit register or

memory location left 1 bit.

RCL reg/mem8,CL

D2 /2

Rotate the 9 bits consisting of the

carry flag and an 8-bit register or

memory location left the number of

bits specified in the CL register.