AMD Confidential

User Manual September 12

th

, 2008

Appendix A 221

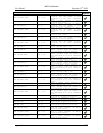

Instruction

Supported

Mnemonic

Opcode

Description

XOR reg16,reg/mem16

33 /r

XOR the contents of a 16-bit

destination register with the

contents of a 16-bit register or

memory operand and store the result

in the destination.

XOR reg32,reg/mem32

33 /r

XOR the contents of a 32-bit

destination register with the

contents of a 32-bit register or

memory operand and store the result

in the destination.

XOR reg64,reg/mem64

33 /r

XOR the contents of a 64-bit

destination register with the

contents of a 64-bit register or

memory operand and store the result

in the destination.

Table 15-8: General-Purpose Instruction Reference

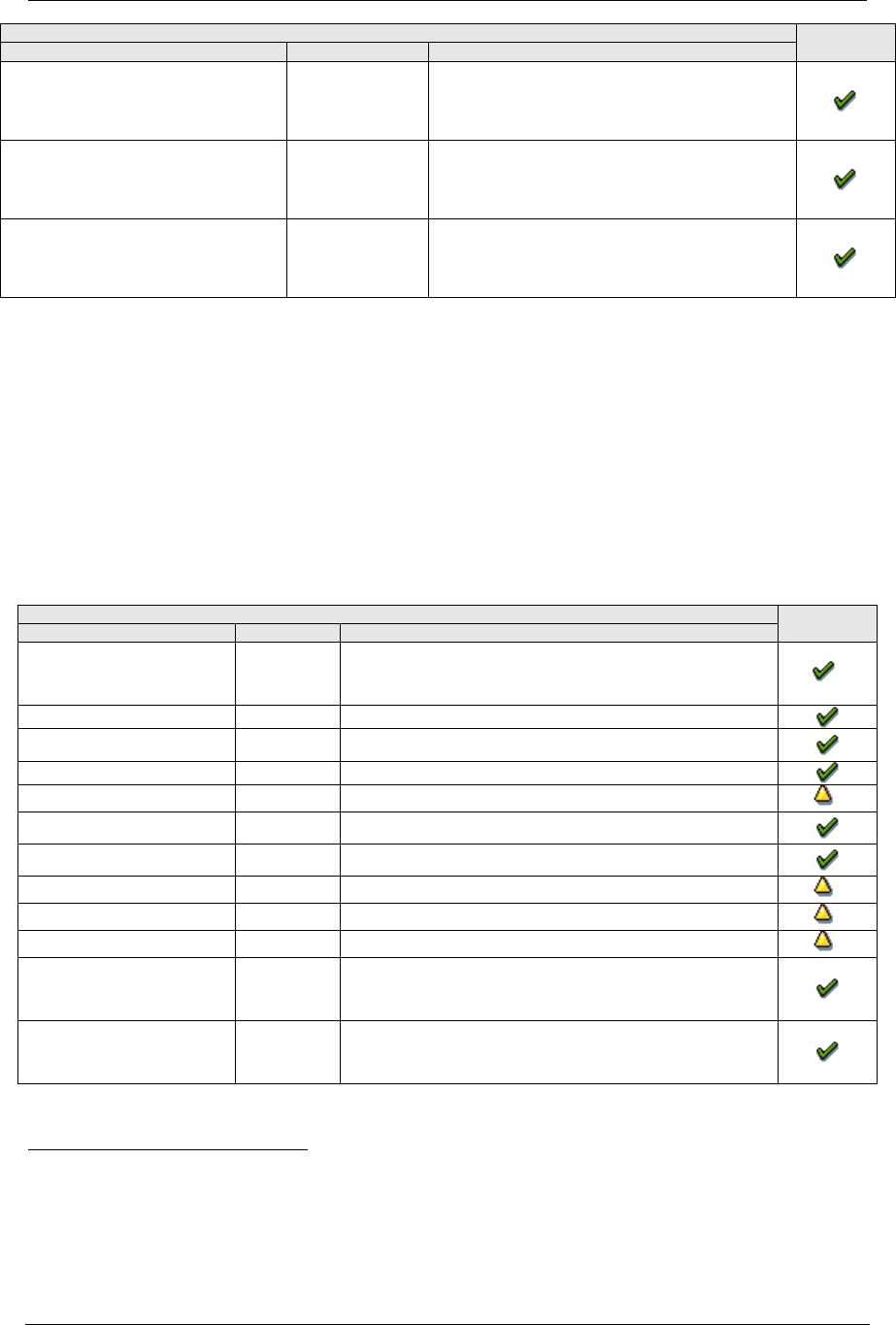

A.6.3 System Instructions

This chapter describes the function, mnemonic syntax and opcodes that the simulator

simulates. The system instructions are used to establish the operating mode, access

processor resources, handle program and system errors, and manage memory. Many of

these instructions can only be executed by privileged software, such as the operating

system kernel and interrupt handlers, that run at the highest privilege level. Only system

instructions can access certain processor resources, such as the control registers, model-

specific register, and debug registers.

Instruction

Supported

Mnemonic

Opcode

Description

ARPL reg/mem16,reg16

63 /r

Adjust the RPL of a destination segment

selector to a level not less than the RPL of

the segment selector specifies in the 16-bit

source register.

1

CLI

FA

Clear the interrupt flag (IF) to zero.

CLTS

0F 06

Clear the task-switched (TS) flag in CR0 to

0.

HLT

F4

Halt instruction execution.

INT 3

CC

Trap to debugger at interrupt 3.

2

INVD

0F 08

Flush internal caches and trigger external

cache flushes.

INVLPG mem8

0F 01 /7

Invalidate the TLB entry for the page

containing a specified memory location.

IRET

CF

Return from interrupt (16-bit operand size).

3

IRETD

CF

Return from interrupt (32-bit operand size).

3

IRETQ

CF

Return from interrupt (64-bit operand size).

3

LAR reg16,reg/mem16

0F 02 /r

Reads the GDT/LDT descriptor referenced by

the 16-bit source operand masks the

attributes with FF00h and saves the result

in the 16-bit destination register.

LAR reg32,reg/mem16

0F 02 /r

Reads the GDT/LDT descriptor referenced by

the 16-bit source operand masks the

attributes with 00FFFF00h and saves the

result in the 32-bit destination register.

1

In 64-bit mode, this opcode (0x63) is used for the MOVSXD instruction.

2

See Section A.6.3.1, “INT – Interrupt to Vector”, on page 203.

3

See Section A.6.3.2, “IRET – Return from Interrupt”, on page 203.