AMD Confidential

User Manual September 12

th

, 2008

Appendix A 215

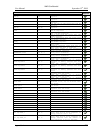

Instruction

Supported

Mnemonic

Opcode

Description

SETNB reg/mem8

0F 93

Set byte if not below (CF = 0).

SETNC reg/mem8

0F 93

Set byte if not carry (CF = 0).

SETAE reg/mem8

0F 93

Set byte if above or equal (CF = 0).

SETZ reg/mem8

0F 94

Set byte if zero (ZF = 1).

SETE reg/mem8

0F 94

Set byte if equal (ZF = 1).

SETNZ reg/mem8

0F 95

Set byte if not zero (ZF = 0).

SETNE reg/mem8

0F 95

Set byte if not equal (ZF = 0).

SETBE reg/mem8

0F 96

Set byte if below or equal (CF = 1 or

ZF = 1).

SETNA reg/mem8

0F 96

Set byte if not above (CF = 1 or ZF =

1).

SETNBE reg/mem8

0F 97

Set byte if not below or equal (CF =

0 and ZF = 0).

SETA reg/mem8

0F 97

Set byte if above (CF = 0 and ZF =

0).

SETS reg/mem8

0F 98

Set byte if sign (SF = 1).

SETNS reg/mem8

0F 99

Set byte if not sign (SF = 0).

SETP reg/mem8

0F 9A

Set byte if parity (PF = 1).

SETPE reg/mem8

0F 9A

Set byte if parity even (PF = 1).

SETNP reg/mem8

0F 9B

Set byte if not parity (PF = 0).

SETPO reg/mem8

0F 9B

Set byte if parity odd (PF = 0).

SETL reg/mem8

0F 9C

Set byte if less (SF <> OF).

SETNGE reg/mem8

0F 9C

Set byte if not greater or equal (SF

<> OF).

SETNL reg/mem8

0F 9D

Set byte if not less (SF =OF).

SETGE reg/mem8

0F 9D

Set byte if greater or equal (SF =

OF).

SETLE reg/mem8

0F 9E

Set byte if less or equal (ZF = 1 or

SF <> OF).

SETNG reg/mem8

0F 9E

Set byte if not greater (ZF = 1 or SF

<> OF).

SETNLE reg/mem8

0F 9F

Set byte if not less or equal (ZF = 0

and SF = OF).

SETG reg/mem8

0F 9F

Set byte if greater (ZF = 0 and SF =

OF).

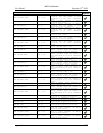

SFENCE

0F AE F8

Force strong ordering of (serialized)

store operations.

SHL reg/mem8,1

D0 /4

Shift an 8-bit register or memory

location left 1 bit.

SHL reg/mem8,CL

D2 /4

Shift an 8-bit register or memory

location left the number of bits

specified in the CL register.

SHL reg/mem8,imm8

C0 /4 ib

Shift an 8-bit register or memory

location left the number of bits

specified by an 8-bit immediate

value.

SHL reg/mem16,1

D1 /4

Shift a 16-bit register or memory

location left 1 bit.

SHL reg/mem16,CL

D3 /4

Shift a 16-bit register or memory

location left the number of bits

specified in the CL register.

SHL reg/mem16,imm8

C1 /4 ib

Shift a 16-bit register or memory

location left the number of bits

specified by an 8-bit immediate

value.

SHL reg/mem32,1

D1 /4

Shift a 32-bit register or memory

location left 1 bit.

SHL reg/mem32,CL

D3 /4

Shift a 32-bit register or memory

location left the number of bits

specified in the CL register.

SHL reg/mem32,imm8

C1 /4 ib

Shift a 32-bit register or memory

location left the number of bits

specified by an 8-bit immediate

value.

SHL reg/mem64,1

D1 /4

Shift a 64-bit register or memory

location left 1 bit.

SHL reg/mem64,CL

D3 /4

Shift a 64-bit register or memory

location left the number of bits

specified in the CL register.