AMD Confidential

User Manual September 12

th

, 2008

Appendix A 223

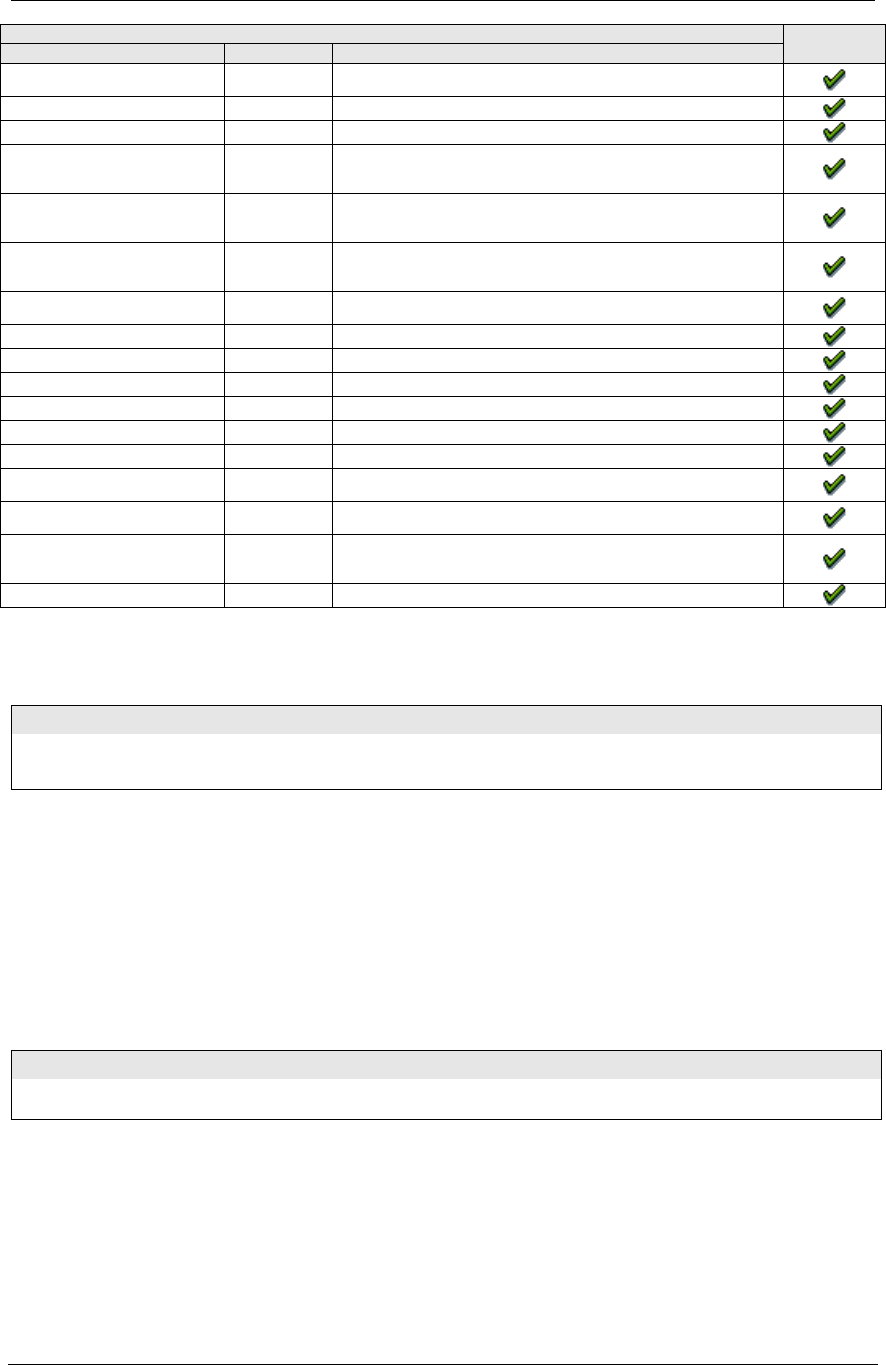

Instruction

Supported

Mnemonic

Opcode

Description

SMSW reg64

0F 01 /4

Store the entire 64 bits of CR0 to a 64-bit

register.

SMSW mem16

0F 01 /4

Store the low 16 bits of CR0 to memory.

STI

FB

Set interrupt flag (IF) to 1.

STR reg16

0F 00 /1

Store the segment selector from the task

register to a 16-bit general-purpose

register.

STR reg32

0F 00 /1

Store the segment selector from the task

register to a 32-bit general-purpose

register.

STR reg64

0F 00 /1

Store the segment selector from the task

register to a 64-bit general-purpose

register.

STR mem16

0F 00 /1

Store the segment selector from the task

register to a 16-bit memory location.

SWAPGS

0F 01 F8

Exchange GS base with KernelGSBase MSR.

SYSCALL

0F 05

Call operating system.

SYSENTER

0F 34

Call operating system.

SYSEXIT

0F 35

Return from operating system.

SYSRET

0F 07

Return from operating system.

UD2

0F 08

Raise an invalid opcode exception.

VERR reg/mem16

0F 00 /4

Set the zero flag (ZF) to 1 if the segment

selected can be read.

VERW

0F 00 /5

Set the zero flag (ZF) to 1 if the segment

selected can be written.

WBINVD

0F 09

Write modified cache lines to main memory,

invalidate internal caches, and trigger

external cache flushes.

WRMSR

0F 30

Write EDX:EAX to the MSR specified by ECX.

Table 15-9: System Instruction Reference

A.6.3.1 INT – Interrupt to Vector

Opcode

Instruction

Description

CD

INT imm8

Interrupt to Vector.

CC

INT 3

Interrupt to Debug Vector.

Interrupt to task-gate is not implemented. An attempt to execute an interrupt to

task-gate results in a „FeatureNotImplemented‟ exception and the simulation will

be stopped.

When delivering an exception in an attempt to deliver a hardware interrupt the

simulation will not push the resume-flag (RF) onto the stack.

Always clears VM, NT, TF, and RF bits in rFLAGS.

A.6.3.2 IRET – Return from Interrupt

Opcode

Instruction

Description

CF

IRET, IRETD,

IRETQ

Return from interrupt

The simulator does not support nested task-switching using the rFLAGS nested-task bit

(NT) and the TSS back-link field. An interrupt return (IRET) to the previous task (nested-

task) will result in a „FeatureNotImplemented‟ exception and the simulation will be

stopped.