Technical Reference Guide

Compaq Personal Computers

Changed –- March 2000

C-3

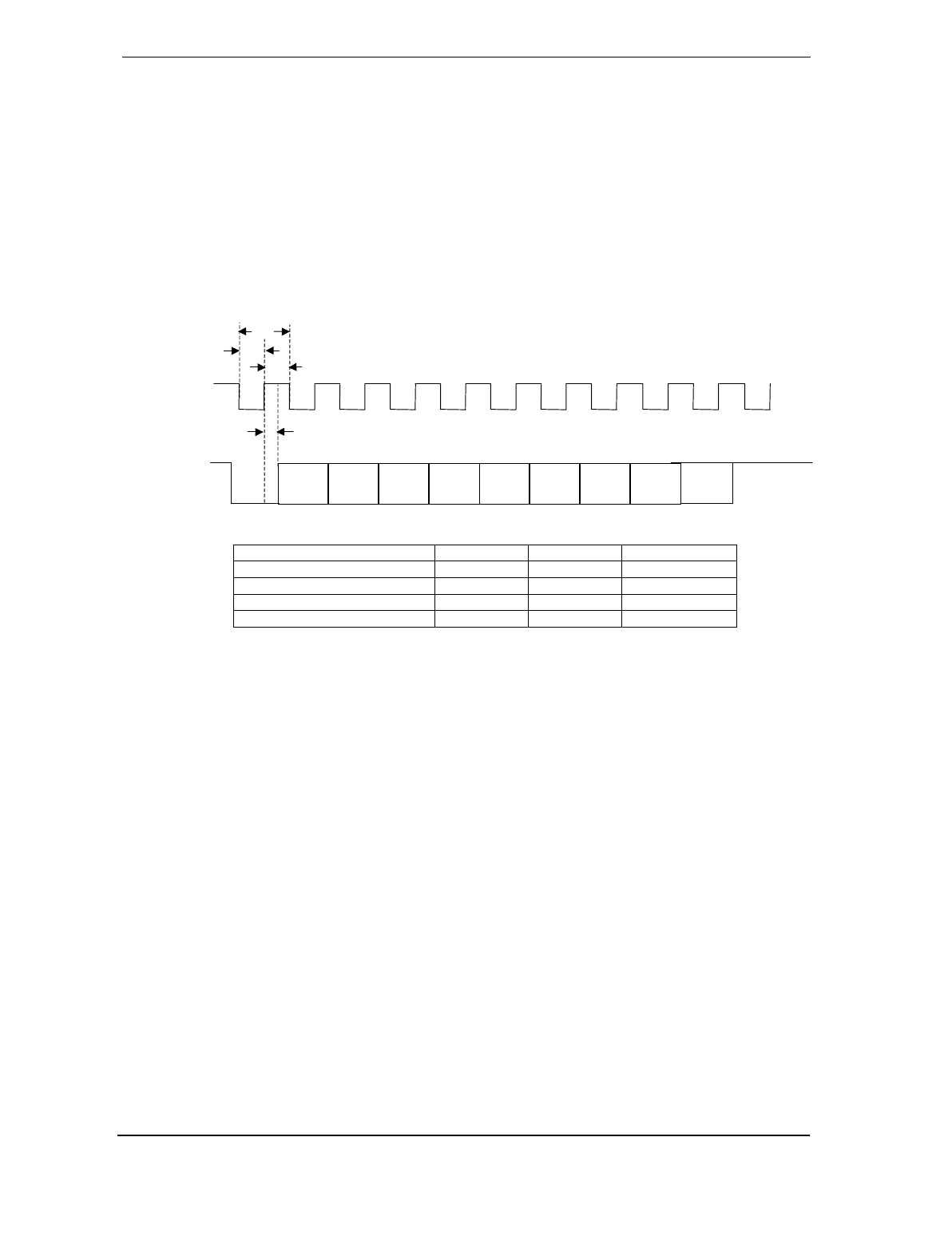

C.2.1 PS/2-TYPE KEYBOARD TRANSMISSIONS

The PS/2-type keyboard sends two main types of data to the system; commands (or responses to

system commands) and keystroke scan codes. Before the keyboard sends data to the system

(specifically, to the 8042-type logic within the system), the keyboard verifies the clock and data

lines to the system. If the clock signal is low (0), the keyboard recognizes the inhibited state and

loads the data into a buffer. Once the inhibited state is removed, the data is sent to the system.

Keyboard-to-system transfers (in the default mode) consist of 11 bits as shown in Figure C-2.

Parameter Minimum Nominal Maximum

Tcy (clock cycle) 60 us -- 80 us

Tcl (clock low) 30 us 41 us 50 us

Tch (clock high) 30 us -- 40 us

Th-t-t (high-before-transmit) -- 20 us --

Figure C–2.

PS/2

Keyboard-To-System Transmission, Timing Diagram

The system can halt keyboard transmission by setting the clock signal low. The keyboard checks

the clock line every 60 us to verify the state of the signal. If a low is detected, the keyboard will

finish the current transmission

if

the rising edge of the clock pulse for the parity bit has not

occurred. The system uses the same timing relationships during reads (typically with slightly

reduced time periods).

The enhanced keyboard has three operating modes:

♦

Mode 1 - PC-XT compatible

♦

Mode 2 - PC-AT compatible (default)

♦

Mode 3 - Select mode (keys are programmable as to make-only, break-only, typematic)

Modes can be selected by the user or set by the system. Mode 2 is the default mode. Each mode

produces a different set of scan codes. When a key is pressed, the keyboard processor sends that

key’s make code to the 8042 logic of the system unit. The When the key is released, a release

code is transmitted as well (except for the Pause key, which produces only a make code). The

8042-type logic of the system unit responds to scan code reception by asserting IRQ1, which is

processed by the interrupt logic and serviced by the CPU with an interrupt service routine. The

service routine takes the appropriate action based on which key was pressed.

Tcy

Th-b-t

Clock

Tcl

Tch

Data

(LSb) (MSb)

Parity

Bit

Data

0

Start

Bit

Data

1

Data

2

Data

3

Data

4

Data

5

Data

5

Data

7

Stop

Bit