Technical Reference Guide

Compaq iPAQ Family of Internet Devices

First Edition - March 2000

5-7

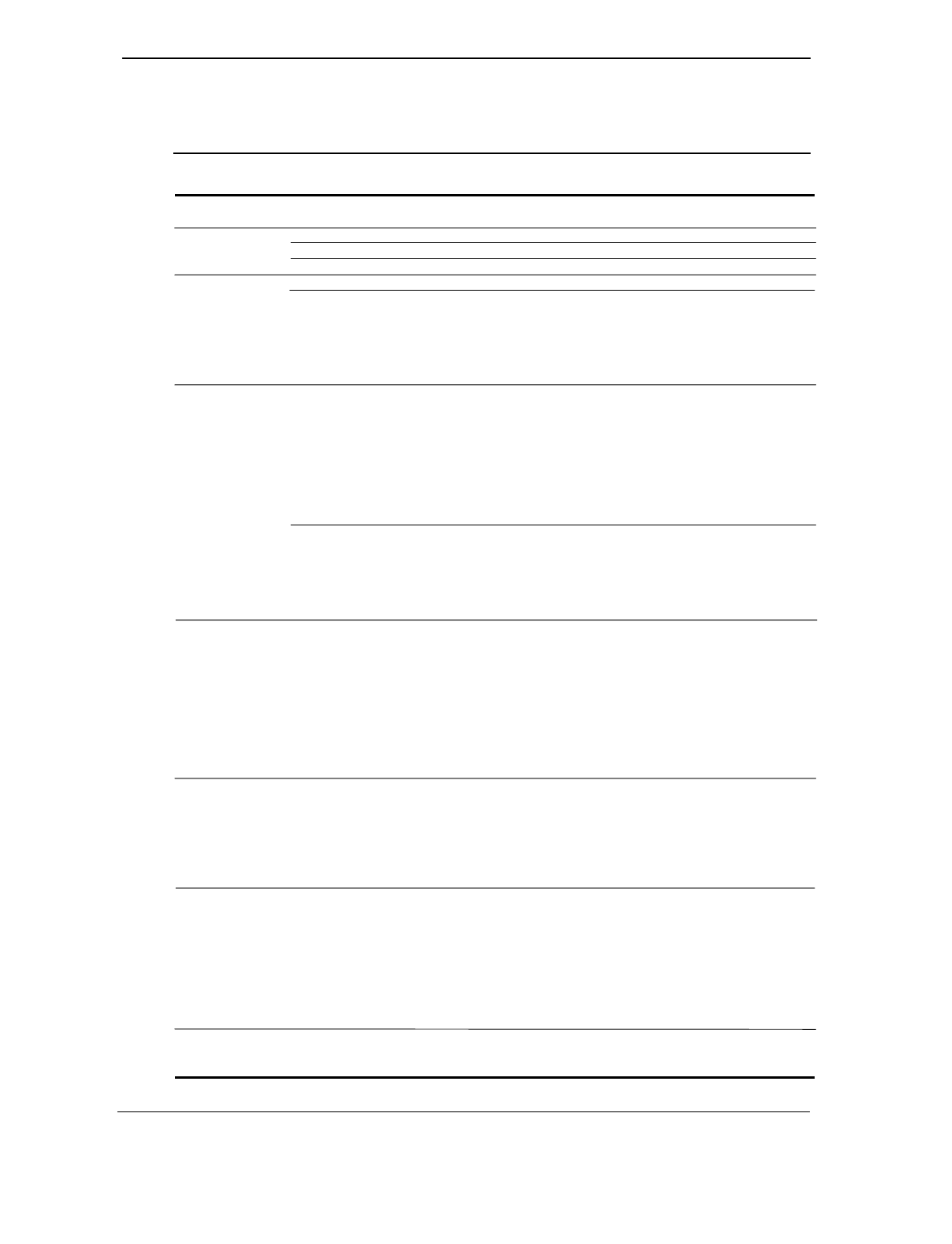

Table 5–7

. Serial Interface Control Registers

Table 5-7.

Serial Interface Control Registers

COM1

Addr.

COM2

Addr. Register R/W

3F8h 2F8h Receive Data Buffer

Transmit Data Buffer

Baud Rate Divisor Register 0 (when bit 7 of Line Control Reg. Is set)

R

W

W

3F9h 2F9h Baud Rate Divisor Register 1 (when bit 7 of Line Control Reg. Is set)

Interrupt Enable Register:

<7..4> Reserved (always 0’s)

<3> Modem status interrupt enable (active high) (CTS, DSR, RI, CD)

<2> Rx line status interrupt enable (active high) (Overrun, parity, framing error)

<1> Tx holding register empty interrupt enable (active high)

<0> Baud rate divisor interrupt enable (active high)

W

R/W

3FAh 2FAh Interrupt ID Register:

<7,6> FIFO Enable/Disable: 0 = disable, 1 = enable

<5,4> Reserved

<3..1> Interrupt Source:

000 = Modem status 100,101 = Reserved

001 = TX holding reg. Empty 110 = Character time-out

010 = RX data available 111 = Reserved

011 = RX line status

<0> Interrupt pending (if cleared)

FIFO Control Register:

<7,6> RX Trigger Level: 00 = 1 byte, 01 = 4 bytes, 10 = 8 bytes, 11 = 14 bytes

<5..3> Rerserved

<2> TX FIFO reset (active high)

<1> RX FIFO reset (active high)

<0> FIFO Enable/Disable: 0 = Disable TX/RX FIFO’s, 1 = Enable TX/RX FIFO’s

R

W

3FBh 2FBh Line Control Register:

<7> Register acces control:

0 = RX buffer, TX holding, divisor rate registers are accessable.

1 = Divisor rate register is accessable

<6> Break control (forces SOUT singla low if set)

<5> Stick parity (if set, even parity bit is 0, odd parity bit is 1)

<4> Parity type: 0 = odd, 1 = even

<3> Parity enable: 0 = disabled, 1 = enabled

<2> Stop bit: 0 = 1 stop bit, 1 = 2 stop bits

<1,0> Word size: 00 = 5 bits, 01 = 6 bits, 10 = 7 bits, 11 = 8 bits

R/W

3FCh 2FCh Modem Control Register:

<7..5> Reserved

<4> Internal loopback enabled (if set)

<3> Serial I/F interrupts enabled (if set)

<2> Reserved

<1> RTS signal active (if set)

<0> DTR signal active (if set)

R/W

3FDh 2FDh Line Status Register:

<7> Parity error, framing error, or Break condition (if set)

<6> TX holding and TX shift registers are empty (if set)

<5> TX holding register is empty (if set)

<4> Break interrupt has occurred (if set)

<3> Framing error has occurred (if set)

<2> Parity error has occurred (if set)

<1> Overrun error has occurred (if set)

<0> Data register ready to be read (if set)

R

3FEh 2FEh Modem Status:

<7..4> DCD-, RI-, DSR, CTS (respectively) active (if set)

<3..0> DCD-, RI-, DSR, CTS (respectively) changed state since last read (if set)

R