Chapter 4 System Support

Compaq iPAQ Family of Internet Devices

First Edition - March 2000

4-4

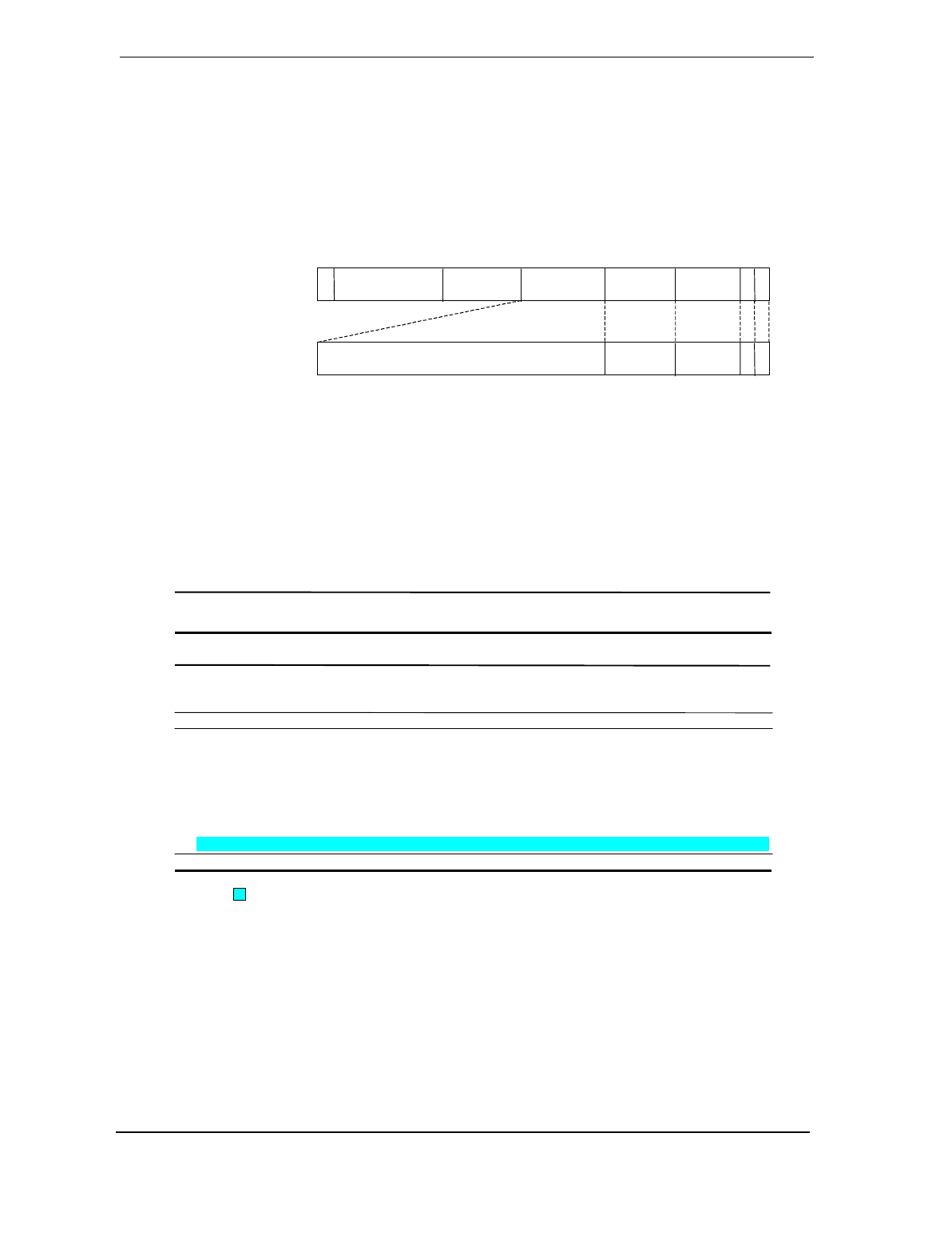

Figure 4-2 shows how the loading of 0CF8h results in a Type 0 configuration cycle on the PCI

bus. The Device Number (bits <15..11> determines which one of the AD31..11 lines is to be

asserted high for the IDSEL signal, which acts as a “chip select” function for the PCI device to be

configured. The function number (CF8h, bits <10..8>) is used to select a particular function

within a PCI component.

Figure 4-2.

Type 0 Configuration Cycle

Type 0 configuration cycles are used for configuring devices on PCI bus # 0. Type 1

configuration cycles (reg. 0CF8h bits <1,0> = 01b) are passed on to PCI bus # 1. Table 4-1 shows

the standard configuration of device numbers for components and slots residing on a PCI bus.

Table 4-1.

PCI Device Configuration Access

Table 4-1.

PCI Component Configuration Access

PCI Component Function # Device #

PCI

Bus #

82810e GMCH:

Memory Controller

AGP Bridge

0

0

0 (00h)

1(01h)

0

0

AGP slot 0 0 (00h) 2

82801 ICH:

PCI Bridge

LPC Bridge

EIDE Controller

USB I/F

SMBus Controller

AC97 Audio Controller

AC97 Modem Controller

0

0

1

2

3

5

6

30 (1Eh)

31 (1Fh)

31 (1Fh)

31 (1Fh)

31 (1Fh)

31 (1Fh)

31 (1Fh)

0

0

0

0

0

0

0

82559 Network I/F Controller 0 2 (02h) 1

NOTES:

Not implemented.

AD31..0

w/Type 0

Config. Cycle

Reserved

Device

Number

Function

Number

Register

Index

Bus

Number

3130 24 23

16 15 11 10 8 721 0

0 0

IDSEL (only one signal line asserted)

Function

Number

Register

Index

31

11 10 8

721 0

Register 0CF8h

Results in: